# Design and Performance Analysis of a CMOS Amplifier for Ultra-Wide Band Wireless Receivers Using Substrate Integrated Waveguide Resonator

$\mathbf{B}\mathbf{y}$

# Mohammad Mahmudul Hasan Tareq Student ID: 17MEE006P

A thesis submitted in partial fulfilment of the requirements for the degree of M.Sc. in EEE

Department of EEE

CHITTAGONG UNIVERSITY OF ENGINEERING AND TECHNOLOGY

MAY 2024

### Declaration

I hereby declare that the work contained in this thesis has not been previously submitted to meet requirements for an award at this or any other higher education institution. To the best of my knowledge and belief, the thesis contains no material previously published or written by another person except where due reference is cited.

**Signature and Date**

\_\_\_\_\_

Mohammad Mahmudul Hasan Tareq

17MEE006P

Department of EEE

Chittagong University of Engineering & Technology (CUET)

i

### List of Publications

#### Conference

- O Publication 1: M. M. H. Tareq, N. Jahan and Q. D. Hossain, "Design of a Millimetre-wave Band LNA Using SIW Resonator in 180-nm CMOS Technology," 2023 6th International Conference on Electrical Information and Communication Technology (EICT), Khulna, Bangladesh, 2023, pp. 1-5, Doi: 10.1109/EICT61409.2023.10427849.

- Publication 2: M. M. H. Tareq, N. Jahan and Q. D. Hossain, "Enhancing Low Noise Amplifiers: A Comparative Study of Substrate Integrated Waveguide Resonators and Traditional Inductors in 180 – nm CMOS Technology" (Under processing)

## Approval by the Supervisor

This is to certify that **Mohammad Mahmudul Hasan Tareq** has carried out this work under my supervision, and that he has fulfilled relevant Academic Ordinance of the Chittagong University of Engineering and Technology, so that he is qualified to submit the following thesis in application for the degree of M.Sc. in EEE.

Dr. Quazi Delwar Hossain

Professor

Department of EEE

Chittagong University of Engineering & Technology

### Acknowledgment

I would like to express my sincere gratitude to my supervisor, Dr. Quazi Delwar Hossain, Professor of the Department of Electrical and Electronic Engineering (EEE) at Chittagong University of Engineering and Technology (CUET). His guidance, unwavering support, and insightful feedback have been invaluable throughout the entire process of my M.Sc. thesis. His expertise and dedication have greatly enriched my research experience.

I am also indebted to my co-supervisor, Dr. Nusrat Jahan, Associate Professor of EEE at CUET, for her valuable contributions and assistance. Her constructive feedback and encouragement have played a pivotal role in shaping the outcome of this research.

I extend my heartfelt thanks to the faculty members of the EEE department at CUET for their intellectual support and inspiration. I am grateful to my peers and friends for their camaraderie and encouragement.

Lastly, I would like to express my deepest appreciation to my family for their unwavering support, understanding, and encouragement throughout this academic journey. Their love and belief in my abilities have been a constant source of motivation.

I am truly grateful to everyone who has played a part, directly or indirectly, in the completion of my M.Sc. thesis.

.

### **Abstract**

This research introduces a novel approach to the design of an ultra-wideband (UWB) low noise amplifier (LNA) by leveraging the substrate integrated waveguide (SIW) resonator. The proposed inductor less LNA operates in the frequency range of 67.5 GHz to 71.5 GHz, strategically aligning with the 180 nm technology transition frequency (fT). The distinct high-quality factor (Q) characteristic inherent in SIW resonators is harnessed to achieve a commendable gain ( $|S_{21}|$ ) at the designated operating frequencies.

Central to the advancement of this LNA design is the seamless integration of SIW resonators, a departure from conventional approaches employing active spiral inductors. This departure marks a pioneering effort in the application of SIW in complementary metal-oxide-semiconductor (CMOS) LNA design, thereby eliminating the need for active spiral inductors and opening new avenues for enhanced performance.

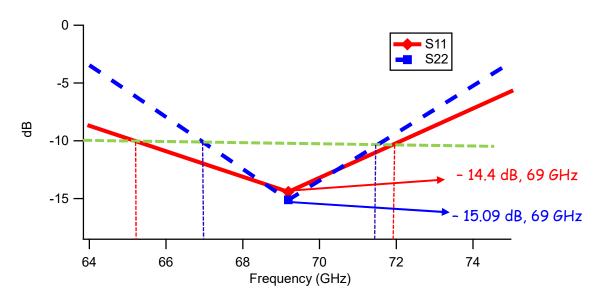

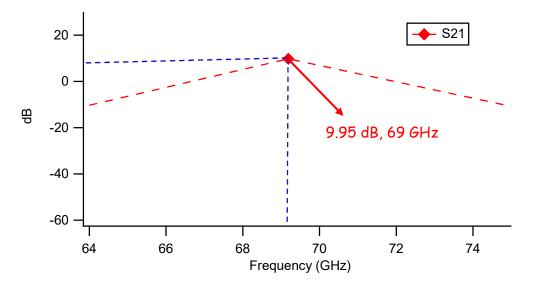

To further enhance the noise performance of the LNA, a sophisticated noise canceller circuit is introduced. This integrated common source and common gate topology, intricately blended with the original common gate configuration, significantly contributes to noise reduction. The judicious incorporation of the noise canceller circuit not only maintains an excellent input match ( $|S_{11}| < -14$  dB) and output match ( $|S_{22}| < -15$  dB) but also contributes to an average noise figure of 8.3 dB and a power gain of 9.76 dB at 69 GHz.

The significance of this work extends beyond the mere introduction of an inductor-less SIW-based LNA. The utilization of SIW resonators brings forth a technological milestone in CMOS LNA design. By eliminating the active spiral inductor, the proposed LNA achieves a delicate balance between gain, noise performance, and frequency compatibility. This research represents a breakthrough, opening new avenues for the application of SIW in high-frequency electronics and advancing the frontiers of CMOS LNA design.

In conclusion, this study not only presents a technologically innovative inductorless SIW-based UWB LNA but also underscores the potential of SIW resonators in revolutionizing the landscape of CMOS LNA design. The findings contribute to the ongoing discourse in high-frequency electronics and pave the way for further exploration and refinement in future research endeavours.

### সারাংশ

এই গবেষণাটি সাবস্ট্রেট ইন্টিগ্রেটেড রেজোনেটর ব্যবহারের মাধ্যমে লো-নয়েজ অ্যামপ্লিফায়ার ডিজাইনের একটি ব্যতিক্রমধর্মী প্রচেষ্টা সম্পর্কে ধারণা দেয়। ১৮০ ন্যানোমিটার প্রযুক্তির সাথে সামঞ্জস্যপূর্ণ প্রস্তাবিত এই ইন্ডাক্টর-বিহীন লো-নয়েজ অ্যামপ্লিফায়ারটি ৬৭.৫ থেকে ৭১.৫ গিগাহার্টজ কম্পাংক সীমার ভেতরে কাজ করে। সাবস্ট্রেট ইন্টিগ্রেটেড রেজোনেটর এর সহজাত উচ্চ কোয়ালিটি ফ্যাক্টরকে কাজে লাগিয়ে উপরোক্ত কম্পাংক সীমার মধ্যে উল্লেখযোগ্য বিবর্ধন অর্জন করা হয়েছে।

এই লো-নয়েজ অ্যামপ্লিফায়ার ডিজাইনের মূল বিষয় হলো সাবস্ট্রেট ইন্টিগ্রেটেড রেজোনেটর এর নিখুঁত ব্যবহার, যেটি ইন্ডাক্টর ব্যবহারকারী গতানুগতিক ডিজাইনগুলো থেকে ব্যতিক্রমধর্মী। এই লো-নয়েজ অ্যামপ্লিফায়ারটি কমপ্লিমেন্টারি মেটাল অক্সাইড সেমিকন্ডাক্টর এ লো-নয়েজ অ্যামপ্লিফায়ার ডিজাইনের ক্ষেত্রে সাবস্ট্রেট ইন্টিগ্রেটেড রেজোনেটর এর প্রয়োগের একটি যুগান্তকারী প্রচেষ্টা, যার ফলে ইন্ডাক্টর ব্যবহারের প্রয়োজন ফুরোবে এবং আরও ভালো ফলাফলের নতুন দিগন্ত উন্মোচিত হবে।

এই লো-নয়েজ অ্যামপ্লিফায়ারটির নয়েজের ফলাফল আরও উন্নত করতে একটি জটিল নয়েজ কেন্সেলার সার্কিটের ধারণা দেয়া হয়েছে। কমন গেইট কনফিগারেশনের সাথে সূক্ষভাবে মিশ্রিত এই ইন্টিগ্রেটেড কমন সোর্স এবং কমন গেইট পদ্ধতিটি নয়েজ কমাতে উল্লেখযোগ্য ভূমিকা পালন করে। নয়েজ কেন্সেলার সার্কিটটির এই সুচিন্তিত ব্যবহার কেবল অসাধারণ ইনপুট ম্যাচিং (এস্১১<— ১৪) এবং আউটপুট ম্যাচিং (এস্২২<— ১৫) ই বজায় রাখে না, উপরন্ধ ৬৯ গিগাহার্টজ কম্পাংকে গড়ে নয়েজ ফিগার এর মান ৮.৩ ডেসিবল এবং পাওয়ার গেইন ৯.৭৬ ডেসিবল রাখতে সহায়তা করে।

এই গবেষণার তাৎপর্য হল ইন্ডাক্টরবিহীন সাবস্ট্রেট ইন্টিগ্রেটেড রেজোনেটর ভিত্তিক লো-নয়েজ অ্যামপ্লিফায়ার-এর সাথে পরিচিত করা। কমপ্লিমেন্টারি মেটাল অক্সাইড সেমিকন্ডাক্টর এ লো-নয়েজ অ্যামপ্লিফায়ার ডিজাইনে সাবস্ট্রেট ইন্টিগ্রেটেড রেজোনেটর এর ব্যবহার প্রযুক্তিগত মাইলফলক বয়ে আনবে। ইন্ডাক্টর এর প্রয়োজনীয়তাকে দূর করার মাধ্যমে প্রস্তাবিত লো-নয়েজ অ্যামপ্লিফায়ারটি গেইন, নয়েজ এবং কম্পাংক এর মাঝে সামঞ্জস্য বজায় রাখতে সক্ষম হবে। এই গবেষণাটি উচ্চ কম্পাংক ইলেক্ট্রনিক্সের ক্ষেত্রে সাবস্ট্রেট ইন্টিগ্রেটেড রেজোনেটর প্রয়োগের ক্ষেত্রে একটি মাইলফলক, যা উন্মোচন করবে নতুন সম্ভাবনার দ্বার এবং কমপ্লিমেন্টারি মেটাল অক্সাইড সেমিকন্ডাক্টর এ লো-নয়েজ অ্যামপ্লিফায়ার ডিজাইনের ক্ষেত্রে অগ্রপথিক হিসেবে ভূমিকা রাখবে।

পরিশেষে, এই গবেষণাটি কেবল প্রযুক্তিগতভাবে নতুন এবং ব্যতিক্রমধর্মী একটি ইন্ডাক্টর-বিহীন সাবস্ট্রেট ইন্টিগ্রেটেড রেজোনেটর ভিত্তিক আল্ট্রা ওয়াইড ব্যান্ড সম্পন্ন লো-নয়েজ অ্যামপ্লিফায়ার-এর ধারণাই দেয় না বরং কমপ্লিমেন্টারি মেটাল অক্সাইড সেমিকন্ডাক্টর এ লো-নয়েজ অ্যামপ্লিফায়ার ডিজাইনের ক্ষেত্রে সাবস্ট্রেট ইন্টিগ্রেটেড রেজোনেটর এর গুরুত্বকেও তুলে ধরে। এই গবেষণালব্ধ ফলাফল চলমান উচ্চ কম্পাংক ইলেক্ট্রনিক্সের গবেষণায় নতুন সংযোজন হবে এবং ভবিষ্যতে আরও নতুন নতুন গবেষণার ক্ষেত্রে পথপ্রদর্শক হিসেবে কাজ করবে।

# **Table of Contents**

| Abst | tract                                                                  | v     |

|------|------------------------------------------------------------------------|-------|

| সারা | ংশ                                                                     | vi    |

| Tabl | e of Contents                                                          | . vii |

| List | of Figures                                                             | ix    |

|      | of Tables                                                              |       |

|      | of Symbols                                                             |       |

|      | •                                                                      |       |

|      | of Abbreviations                                                       |       |

| 1 I1 | ntroduction                                                            | 15    |

| 1.1  | Background                                                             | . 15  |

| 1.2  | Motivation                                                             | . 15  |

|      | 1.2.1 Operational Amplifiers (OP-AMPs) in UWB Systems                  | . 16  |

|      | 1.2.2 The Prospects of Substrate Integrated Waveguide (SIW) Resonators | . 18  |

|      | 1.2.2.1 Planar Structure and Wave Propagation                          | 18    |

|      | 1.2.2.2 Resonance in SIW                                               |       |

|      | 1.2.2.3 High-Quality Factor (Q-factor)                                 |       |

|      | 1.2.2.4 Compatibility with Integrated Circuit Technology               |       |

|      | 1.2.2.5 Enhancements in Bandwidth and Gain                             |       |

|      | 1.2.2.6 Noise Reduction                                                |       |

|      | 1.2.3 LNA Fundamental                                                  | . 20  |

|      | 1.2.4 Importance of Low Noise                                          | . 20  |

|      | 1.2.4.1 Inherent Weakness of Received Signals                          |       |

|      | 1.2.4.2 Noise Figure and Noise Temperature                             |       |

|      | 1.2.4.3 Preservation of Signal Integrity                               |       |

|      | 1.2.4.4 Signal-to-Noise Ratio (SNR) Considerations                     |       |

|      | 1.2.5 Gain and Bandwidth                                               | . 23  |

|      | 1.2.6 Transistor Selection and Biasing                                 | . 24  |

|      | 1.2.7 Matching Networks and Impedance Matching                         | . 25  |

|      | 1.2.8 Stability and Linearity                                          | . 25  |

|      | 1.2.9 Power Consumption                                                | . 26  |

| 1.3  | Objective of the Thesis                                                | . 27  |

| 1.4  | Significance and Scope                                                 | . 27  |

| 1.5  | Thesis Outline                                                         | 28    |

| 2 F  | undamentals of LNA                                                     | 30    |

| 2.1  | S Parameters                                                           |       |

|      |                                                                        |       |

| 2.2  | Performance Matrices of LNA                                            |       |

|      | 2.2.1 Gain of Power and Impedance Alignment                            |       |

|      | 2.2.2 Noise Figure                                                     | 33    |

|     | 2.2.3 Electrical Power Utilization                    | 36 |

|-----|-------------------------------------------------------|----|

|     | 2.2.4 Linearity                                       |    |

|     | 2.2.5 Stability                                       | 38 |

| 3 L | iterature Review                                      | 41 |

| 3.1 | Wideband LNA Implementation Approaches                | 41 |

| 3.2 | Common Source with Resistive Termination LNA Topology | 43 |

| 3.3 | Common Gate Topology                                  |    |

| 3.4 | Feedback LNA Topologies                               | 46 |

|     | 3.4.1 Resistive Feedback LNA Topology                 |    |

|     | 3.4.1.1 Gain Analysis                                 |    |

|     | 3.4.1.2 Noise Figure Analysis                         |    |

|     | 3.4.3 Active Feedback LNA                             |    |

| 3.5 | Distributed Amplifier LNA Topology                    |    |

| 4 L | JWB LNA Design and Optimization                       |    |

| 4.1 | Design of SIW Resonator                               |    |

|     | 4.1.1 Performance of the proposed SIW                 |    |

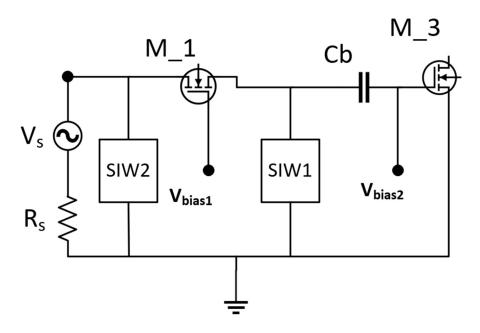

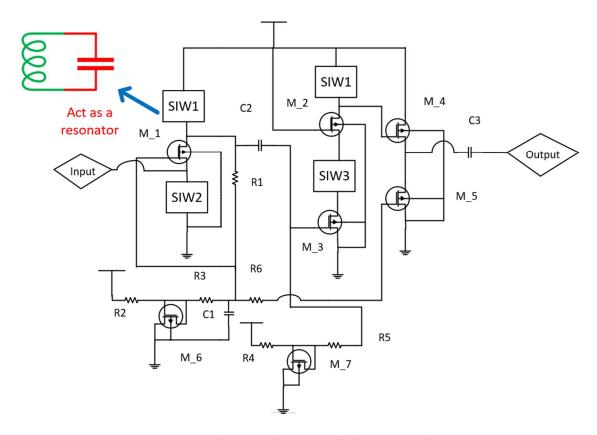

| 4.2 | Diagrammatic Representation of the LNA                | 64 |

|     | 4.2.1 Input matching                                  |    |

|     | 4.2.2 Gain Analysis and Variable Gain Mechanism       | 69 |

|     | 4.2.3 Noise Analysis and Optimization                 | 69 |

| 4.3 | Schematic of the Proposed LNA                         | 72 |

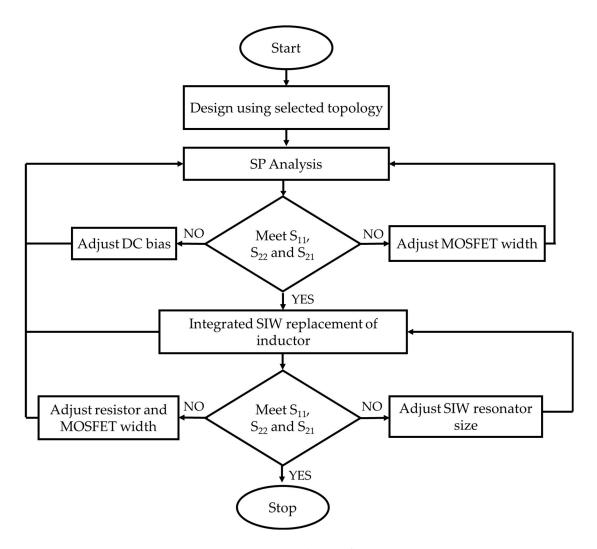

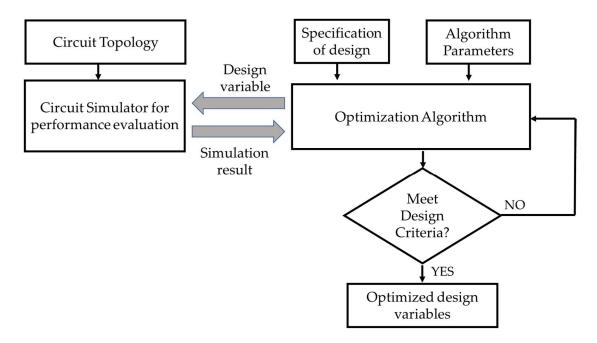

| 4.4 | Design Optimization                                   | 76 |

| 4.5 | Simulation Result and Discussion                      | 78 |

| 5 C | Conclusions & Future Work                             | 85 |

| 5.1 | Conclusions and Major Contribution                    | 85 |

| 5.2 | Implications and Future Directions                    | 86 |

| D.1 | liography                                             | 87 |

# **List of Figures**

| Figure 1.1: Applications of UWB                                                                                                                | 16    |

|------------------------------------------------------------------------------------------------------------------------------------------------|-------|

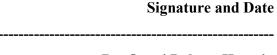

| Figure 1.2: Basic symbol of an Op-amp                                                                                                          | 17    |

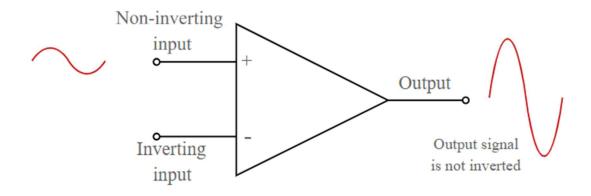

| Figure 1.3: Fabricated SIW Resonator                                                                                                           | 18    |

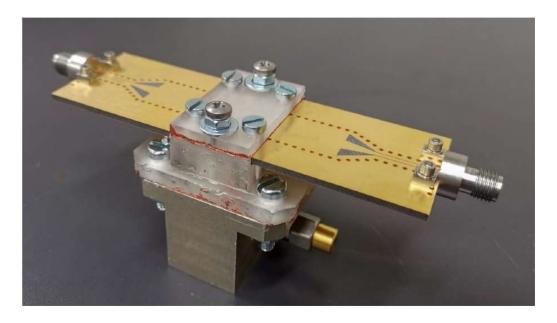

| Figure 2.1: Two-port Network                                                                                                                   | 30    |

| Figure 2.2: MOSFET channel thermal noise representation                                                                                        | 34    |

| Figure 2.3: Equivalent noise model for gate resistance                                                                                         | 35    |

| Figure 2.4: 1 dB compression point                                                                                                             | 37    |

| Figure 3.1: (a) Resistive termination, (b) Common gate, (c) Feedback LNA topology                                                              | 42    |

| Figure 3.2: (a) Filter, (b) Distributed LNA topology                                                                                           | 42    |

| Figure 3.3: Common Source (CS) with resistive termination topology                                                                             | 43    |

| Figure 3.4: AC equivalent circuit with noise sources of resistive termination                                                                  | CS 43 |

| Figure 3.5: Common Gate (CG) topology                                                                                                          | 44    |

| Figure 3.6: Feedback topologies a) resistive b) series RC c) parallel RC and d) transformer                                                    |       |

| Figure 3.7: Resistive feedback common source (CS) topology                                                                                     | 48    |

| Figure 3.8: AC equivalent circuit of resistive feedback CS topology                                                                            | 48    |

| Figure 3.9: AC equivalent circuit with noise sources of resistive feedback CS                                                                  | 49    |

| Figure 3.10: Feedback resistance noise of resistive feedback CS                                                                                | 50    |

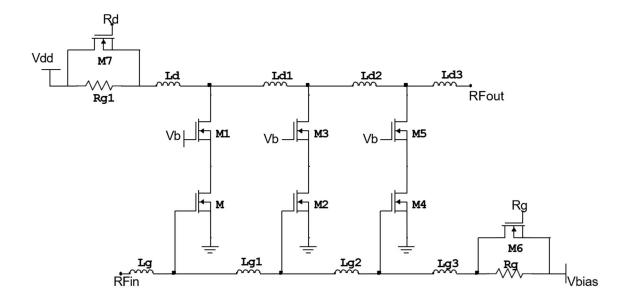

| Figure 3.11: Cascode DA Schematic                                                                                                              | 53    |

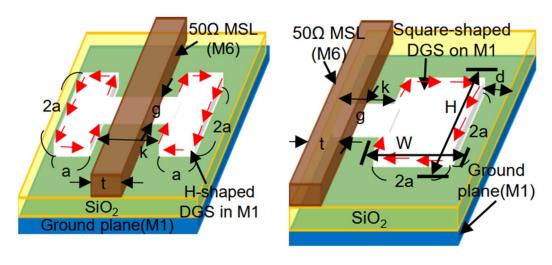

| Figure 3.12: Cross-coupled oscillator with DGS resonator                                                                                       | 54    |

| Figure 3.13: H – shaped and Square – shaped DGS resonator                                                                                      | 54    |

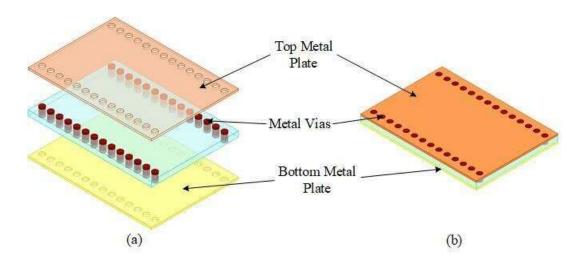

| Figure 3.14: SIW 3D Model (a) Exploded View, (b) Normal View                                                                                   | 55    |

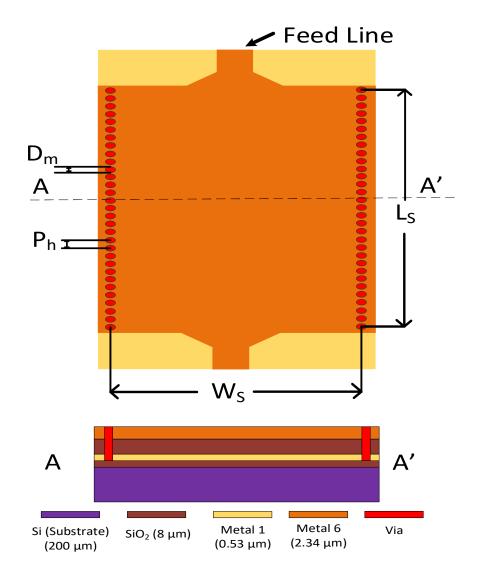

| Figure 4.1: Cross section and schematic diagram of the proposed SIWs                                                                           | 60    |

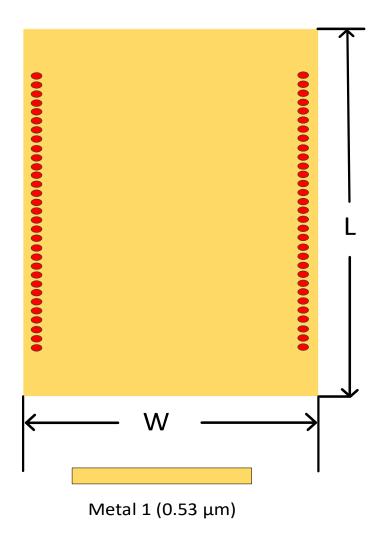

| Figure 4.2: Bottom view the SIWs from metal1                                                                                                   | 61    |

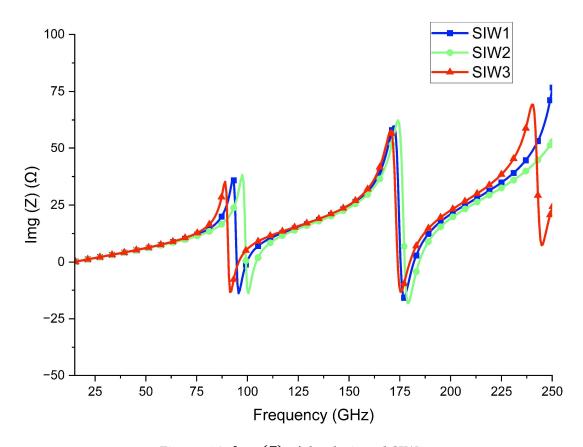

| Figure 4.3: ImgZ of the designed SIWs                                                                                                          | 62    |

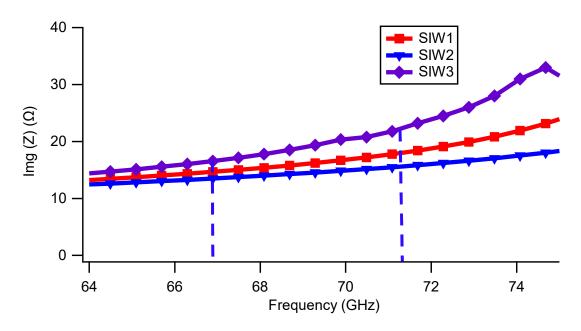

| Figure 4.4: Img(Z) of the designed SIWs for required bandwidth                                                                                 | 63    |

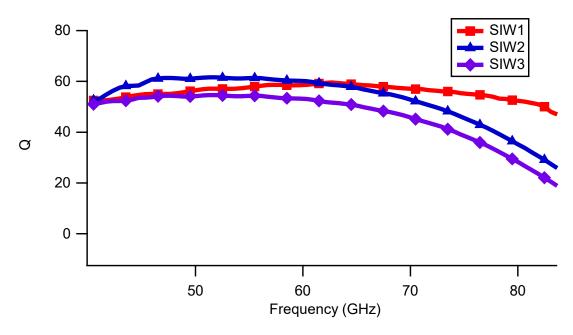

| Figure 4.5: Q factor of the designed SIWs                                                                                                      | 64    |

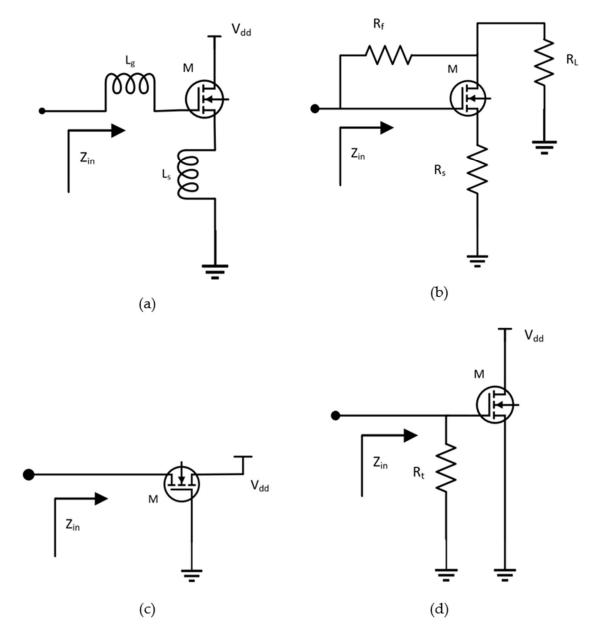

| Figure 4.6: Basic input matching techniques (a) Inductive source degeneration Shunt-series feedback (c) Common-gate 1/g termination (d) Direct | ` '   |

| resistor termination                                                                                                                           |       |

| Figure 4.7: Configuration of a common-gate input stage                                                                                         | 67    |

| Figure 4.8: MOS transistor small-signal model usages in common-gate stage input impedance derivation | 68 |

|------------------------------------------------------------------------------------------------------|----|

| Figure 4.9: MOS transistor noise model including the induced gate noise                              | 70 |

| Figure 4.10: Noise calculation of the common-gate stage cascaded by a common source stage            | 71 |

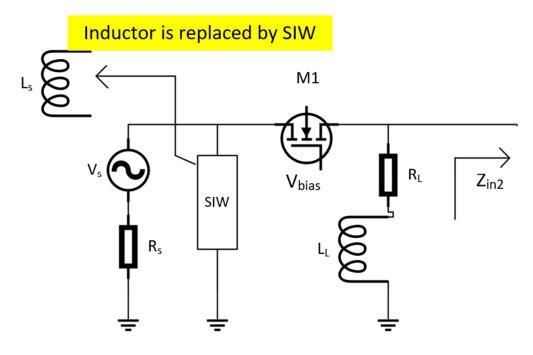

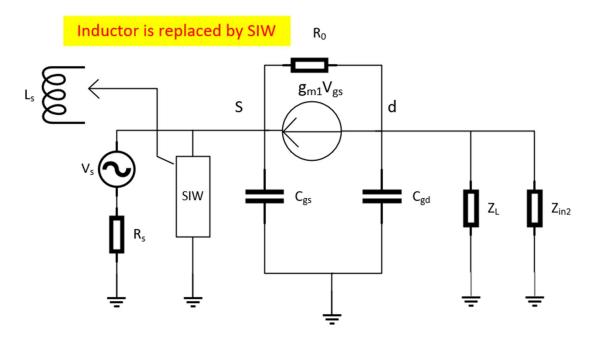

| Figure 4.11: Schematic diagram of the proposed LNA                                                   | 73 |

| Figure 4.12: Performance trade-off of LNA                                                            | 75 |

| Figure 4.13: LNA design flow chart                                                                   | 76 |

| Figure 4.14: LNA design optimization flow chart                                                      | 77 |

| Figure 4.15: Input reflection coefficient and output matching                                        | 78 |

| Figure 4.16: Gain of the proposed LNA                                                                | 79 |

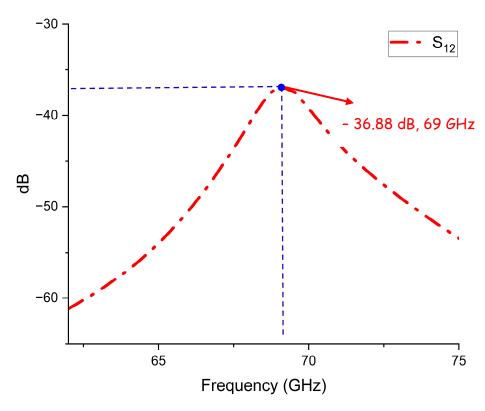

| Figure 4.17: Isolation of the proposed LNA                                                           | 80 |

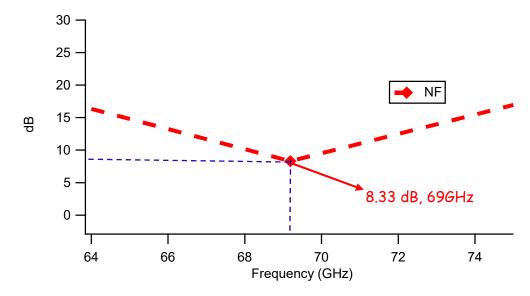

| Figure 4.18: Noise figure of the proposed LNA                                                        | 81 |

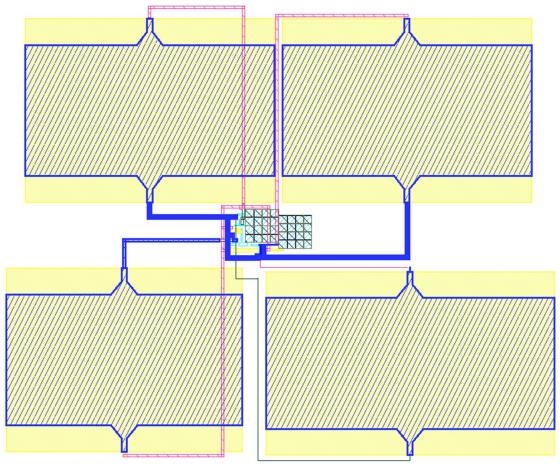

| Figure 4.19: Layout of the proposed LNA                                                              | 82 |

# **List of Tables**

| Table 3.1: Summary of detail literature survey of the wideband LNA | . 56 |

|--------------------------------------------------------------------|------|

| Table 4.1: Parameters of Designed SIWs                             | . 63 |

| Table 4.2: Dimensions of the Proposed LNAs                         | . 74 |

| Table 4.3: Comparison of this work with recent works               | . 83 |

# **List of Symbols**

| Q                | Quality Factor                       |

|------------------|--------------------------------------|

| dB               | Decibel                              |

| $P_{s\_in}$      | Input Signal Power                   |

| $P_{n\_in}$      | Input Noise Power                    |

| $P_{s\_out}$     | Output Signal Power                  |

| $P_{n\_out}$     | Output Noise Power                   |

| K                | Boltzmann's Constant                 |

| T                | Temperature In Kelvin                |

| $\Delta f$       | Bandwidth                            |

| Hz               | Hertz                                |

| $g_{d0}$         | Drain to Source Conductance          |

| $ ho_{sh}$       | Silicide Sheet Resistance            |

| W                | Width of MOSFET                      |

| L                | Length of MOSFET                     |

| $ ho_{con}$      | Polysilicon Contact Resistance       |

| Si               | Silicon Substrate                    |

| SiO <sub>2</sub> | Silicon di-Oxide                     |

| $C_{ox}$         | Gate Oxide Capacitance Per Unit Area |

| $I_{DC}$         | DC Current                           |

| $g_m$            | Transconductance                     |

| GHz              | Giga Hertz                           |

| mW               | Milli-Watt                           |

| mm               | Millimetre                           |

| μm               | Micrometre                           |

| $P_h$            | Distance Between Vias           |

|------------------|---------------------------------|

| $D_m$            | Diameter of Via                 |

| $\lambda_{ m g}$ | Guided Wavelength               |

| C                | Velocity of Light in the Vacuum |

| f <sub>r</sub>   | Design Frequency                |

| Ω                | Ohm                             |

| nm               | Nanometre                       |

# **List of Abbreviations**

| UWB     | Ultra-Wide Band                        |

|---------|----------------------------------------|

| WPANs   | Wireless Personal Area Networks        |

| OP-AMPs | Operational Amplifiers                 |

| GBW     | Gain Bandwidth                         |

| SIW     | Substrate Integrated Waveguide         |

| RF      | Radio Frequency                        |

| LNA     | Low Noise Amplifier                    |

| NF      | Noise Figure                           |

| SNR     | Signal to Noise Ratio                  |

| BJTs    | Bipolar Junction Transistors           |

| FETs    | Field Effect Transistors               |

| IIP3    | Third order Input Interception Point   |

| CS      | Common Source                          |

| CG      | Common Gate                            |

| NMOS    | N-type Metal Oxide Semiconductor       |

| PMOS    | N-type Metal Oxide Semiconductor       |

| MOSFET  | Metal Oxide Semiconductor Field Effect |

| WIGGIEI | Transistor                             |

| DA      | Distributed Amplifier                  |

| DGS     | Defected Ground Structure              |

| FB      | Feed Back                              |

| MOS     | Metal Oxide Semiconductor              |

| PSD     | Power Spectral Density                 |

### 1 Introduction

#### 1.1 Background

During this period of rapid technological growth, the technology of wireless communication plays an essential part in the connections that are made in the modern world. From mobile devices to applications for the Internet of Things, it is becoming increasingly important for a wide variety of devices to have the ability to transfer data effectively and communicate without any interruptions. The tremendous bandwidth capacity of Ultra-Wide Band (UWB) technology makes it a promising alternative for handling the growing demand for broadband internet.

UWB technology has expanded beyond its initial application in radar systems to embrace a variety of different areas, including healthcare, automobile radar, accurate indoor location services, and wireless personal area networks (WPANs). One of the most notable characteristics of UWB is its capacity to transmit data over a broad bandwidth, which enables high transmission speeds and an accurate tracking of location.

#### 1.2 Motivation

UWB technology shows promise but comes with specific challenges, particularly in signal amplification. UWB signals necessitate amplifiers with exceptional bandwidth to operate effectively over a broad frequency range due to their vast frequency range. Designing and implementing amplifiers in UWB systems is made more complex by the need for low noise figure and high linearity. Figure 1.1 depicts the use of UWB in various applications.

Figure 1.1: Applications of UWB [1]

Traditional amplifier designs often do not meet the high-performance requirements of UWB communication due to being optimized for narrower bandwidths. Achieving the challenging technical task of balancing bandwidth, gain, and noise performance requires innovative ideas and advanced technology.

#### 1.2.1 Operational Amplifiers (OP-AMPs) in UWB Systems

Operational Amplifiers (OP-AMPs) play a vital role in signal amplification and conditioning in electronic systems, including UWB communication systems. Designing OP-AMPs for UWB applications poses specific challenges due to the wide frequency range, high gain requirements, and stringent performance specifications. Traditional OP-AMP designs struggle to achieve the desired bandwidth, gain, power consumption, and noise performance necessary for UWB systems.

The design of operational amplifiers for UWB systems requires careful consideration of several factors. One of the main challenges is achieving a wide bandwidth to accommodate the UWB frequency range. Traditional OP-AMP designs often struggle to achieve the necessary gain-bandwidth product (GBW) for UWB applications. Researchers have explored various approaches to overcome this limitation, including the use of multi-stage amplification, distributed amplifiers, and active inductors. Figure 1.2 illustrates the operation and basic symbol of an operational amplifier (Op-amp).

Figure 1.2: Basic symbol of an Op-amp [2]

Another critical consideration is the power consumption of the OP-AMP. UWB systems typically require low-power operation to extend battery life and ensure energy efficiency. Design techniques such as biasing optimization, adaptive biasing, and subthreshold operation have been investigated to minimize power consumption while maintaining acceptable performance.

Additionally, UWB OP-AMPs must exhibit low noise characteristics to preserve the signal integrity and achieve high data rates. Noise optimization techniques, such as noise figure matching, input transistor sizing, and proper biasing, have been explored to mitigate noise contributions and improve overall system performance.

#### 1.2.2 The Prospects of Substrate Integrated Waveguide (SIW) Resonators

The advancement of Substrate Integrated Waveguide (SIW) resonators is a crucial progression in achieving efficient Ultra-Wideband (UWB) expansion. Their unique characteristics, including a high-quality factor (Q-factor) and compatibility with integrated circuit technology, make them an attractive choice for enhancing amplifier performance. Incorporating substrate integrated waveguide (SIW) resonators into the operational amplifier (OP-AMP) design enables achieving high bandwidth, gain, and low noise performance, offering a ground breaking solution to ultra-wideband (UWB) amplification challenges. Fabricated SIW for mm-waveband application is shown in figure 1.3.

Figure 1.3: Fabricated SIW Resonator [3]

#### 1.2.2.1 Planar Structure and Wave Propagation

Provide a detailed explanation of the planar structure of SIW, discussing its fabrication techniques and advantages in terms of miniaturization and ease of integration. Elaborate on guided wave propagation within SIW, emphasizing the confinement of signals within the substrate, reducing radiation losses, and enhancing efficiency.

#### 1.2.2.2 Resonance in SIW

Delve into the physics of resonance in SIW resonators, exploring how the electromagnetic waves interact within the structure to create resonant modes. Discuss the role of parameters such as the width and height of the SIW in determining the resonant frequency, providing a more in-depth understanding.

#### 1.2.2.3 High-Quality Factor (Q-factor)

Define Q-factor in the context of resonators, explaining its role in determining the sharpness of the resonance peak and signal quality. Provide examples of how the high Q-factor of SIW resonators leads to longer ring-down times and better energy storage, crucial for applications demanding signal integrity.

#### 1.2.2.4 Compatibility with Integrated Circuit Technology

Elaborate on the compatibility of SIW resonators with integrated circuits, discussing the fabrication processes involved and the advantages of cointegration. Explore specific examples of successful integration, showcasing the versatility of SIW resonators in various circuit designs. Provide a nuanced understanding of how SIW resonators contribute to radar system performance, considering applications like automotive radar or advanced surveillance. Discuss improvements in range resolution, target discrimination, and overall radar sensitivity.

#### 1.2.2.5 Enhancements in Bandwidth and Gain

Detail how the integration of SIW resonators extends the bandwidth of OP-AMPs, breaking down the technical aspects of bandwidth enhancement through resonator coupling. Discuss the trade-offs involved in gain enhancement, including the consideration of power consumption and stability. Showcase specific wireless communication scenarios where SIW resonators are instrumental, such as in 5G or beyond-5G applications. Discuss the impact on signal coverage, interference mitigation, and the potential for increased data

transfer rates. Explore the intricacies of SIW resonators in biomedical applications, including their role in medical imaging systems, implantable devices, or wireless healthcare monitoring.

#### 1.2.2.6 Noise Reduction

Provide an in-depth analysis of how SIW resonators contribute to noise reduction in OP-AMPs, considering the impact on signal-to-noise ratio (SNR) and overall system performance. Explore design strategies and methodologies employed to achieve optimal noise performance.

Conduct a thorough analysis of current challenges in SIW resonator technology, addressing issues such as manufacturing tolerances, frequency agility, or material limitations. Consider the impact of environmental factors on SIW resonator performance and reliability. Emphasize the transformative impact on amplifier performance, signalling a paradigm shift in addressing UWB amplification challenges.

#### 1.2.3 LNA Fundamental

In the field of radio frequency (RF) and microwave engineering, a Low Noise Amplifier, often known as an LNA, is an essential component. Increasing the strength of weak signals while simultaneously introducing as little noise as possible is its major purpose. In communication systems, low-noise amplifiers (LNAs) serve a crucial function, particularly in situations when the signal that is received is weak. Examples of such situations include wireless receivers and satellite communications services. When it comes to building and optimizing amplifiers for a variety of applications, having a solid understanding of the fundamental concepts of LNAs is absolutely necessary.

#### 1.2.4 Importance of Low Noise

When it comes to the complex landscape of amplifier design, the defining characteristic of a Low Noise Amplifier (LNA) is that it has an uncompromising emphasis on achieving low noise performance. Because of this distinguishing feature, low-noise amplifiers (LNAs) are considered to be vital components, particularly in communication systems, where the fidelity of the signals that are received is automatically vulnerable to a wide variety of problems.

#### 1.2.4.1 Inherent Weakness of Received Signals

Among the many challenges that are encountered in the field of communication systems, one of the most common ones is the inherent fragility of received signals. This vulnerability can be attributable to a wide variety of variables, including the weakening of signals across long distances, the detrimental effects of interference, and the utilization of low-power transmitters. These factors all contribute to the fragility of the structure. When all of these elements come together, the result is a situation in which the incoming signal is not just weak but also susceptible to disturbances from the outside world.

#### 1.2.4.2 Noise Figure and Noise Temperature

There are two metrics that are commonly used to quantify the performance of an LNA. These parameters are known as the noise figure (NF) and the noise temperature (T). The noise figure indicates the performance of an amplifier by comparing its actual noise output to the theoretical minimum noise output, known as the quantum limit. A lower noise figure demonstrates improved performance. On the other hand, noise temperature is a measurement of the amount of thermal noise power that the amplifier contributes to the system. Characterizing noise performance is made easier by the fact that it is stated in Kelvin (K), which is a unit of measurement.

#### 1.2.4.3 Preservation of Signal Integrity

In such scenarios, the necessity for achieving high levels of noise reduction in amplifiers, particularly in low noise amplifiers (LNAs), becomes critically significant. Not only is the amplification of the signal the primary objective, but also the maintenance of the signal's integrity. When it comes to protecting the signal-to-noise ratio (SNR), which is a fundamental measure that defines the

quality of the information that is received, the delicate interaction that occurs between the frequency of the signal and the noise becomes a critical determining factor.

#### 1.2.4.4 Signal-to-Noise Ratio (SNR) Considerations

One of the most important parameters to consider when evaluating the robustness of a communication system is the Signal-to-Noise Ratio, often known as SNR. When the signal-to-noise ratio (SNR) is high, it indicates that the ability to differentiate between signal and noise is higher, which directly translates into improved signal clarity. This delicate equilibrium is put in jeopardy when extra noise is introduced during the process of amplification, which has the potential to compromise the signal's ability to be discerned amidst the background noise.

When it comes to signal amplification, a cautious approach is required because of the inherent fragility of weak signals. Any increase in noise levels that occurs throughout this process has the potential to cause a decrease in the signal-to-noise ratio (SNR), which can then have a domino effect on the overall quality of the information that is received. The reduction in the quality of the information is not only a theoretical worry; rather, it is a concrete result that has implications for the efficiency of the entire communication system.

Because of their dedication to reducing noise, local noise abatement systems (LNAs) have emerged as entities that play an important role in this context. Finding the ideal balance between signal amplification and noise reduction is one of the painstaking design concerns that are inherent in low-noise amplifiers (LNAs). Through the application of advanced engineering, low-noise amplifiers (LNAs) strive to amplify weak signals with the highest possible efficiency while introducing the least amount of additional noise possible. This helps to ensure that the information that is received is accurate and reliable.

#### 1.2.5 Gain and Bandwidth

Gain and bandwidth are crucial factors in determining the effectiveness and performance of a Low Noise Amplifier (LNA) in amplifier design. An LNA's primary function is to minimize noise while also amplifying weak input signals and offering a wide bandwidth to support various frequency ranges in modern communication systems.

The primary function of an LNA is to provide adequate gain. Gain, defined as the ratio of output signal power to input signal power and commonly represented in decibels (dB), is a crucial element in the amplification process. It coordinates the conversion of faint input signals into clear and powerful entities, making them suitable for smooth advancement through following phases in the communication system. Adjusting signal strength with precision through gain is crucial for maintaining signal accuracy throughout transmission despite various challenges.

Gain in amplifier design represents more than just a numerical value; it signifies how efficiently and effectively an LNA increases the strength of incoming signals. Choosing the right gain parameters during the design process is crucial as it determines the trade-off between signal amplification and the risk of adding unwanted noise. This fragile balance showcases the precise engineering needed to attain the best amplification results.

The bandwidth of a Low Noise Amplifier (LNA) is a crucial factor that affects its operational range in addition to the need for profit. Bandwidth refers to the range of frequencies within which the LNA may operate well without any noticeable decrease in performance. In the vast field of modern communication systems, which have various frequency allocations and strict requirements for signal quality across the entire range, the bandwidth of an LNA is a crucial element.

A carefully chosen bandwidth allows for effective signal amplification within a specific frequency range and provides the ability to adjust to changing frequencies. The versatility and application of an LNA in many situations are highlighted by its capability to navigate complex frequency networks in real-world communication scenarios.

The combination of gain, bandwidth, and low noise performance represents the complex balancing required in LNA design. Engineers carefully balance several factors to design an amplifier that efficiently amplifies weak signals and functions smoothly across a specific frequency range. Optimizing gain and bandwidth while maintaining low noise is the epitome of engineering perfection in LNA development.

#### 1.2.6 Transistor Selection and Biasing

Transistor technology selection and precise biasing method are crucial elements in Low Noise Amplifier (LNA) design. Choosing between transistor types like Bipolar Junction Transistors (BJTs) and Field-Effect Transistors (FETs) requires careful evaluation of their specific benefits and drawbacks.

BJTs are well-known for their linearity and strong transconductance, making them ideal for applications that require linear amplification. On the other hand, FETs are favoured in situations where noise performance is more important due to their high input impedance and lower noise figures. Effective decision-making requires a deep comprehension of the application context and a thorough assessment of performance metrics.

The biasing technique functions as a conductor in this orchestration, establishing the best operating points to maintain a precise equilibrium between linearity, gain, and noise performance. Optimal linearity is achieved by managing non-linearities by precise biasing, maintaining signal integrity, and reducing distortions. Regulating gain is closely connected to fine-tuning

accuracy, guaranteeing the amplifier functions within the intended range for the best amplification.

#### 1.2.7 Matching Networks and Impedance Matching

In amplifier design, matching networks play a crucial role by aligning the input and output impedances of the Low Noise Amplifier (LNA) with surrounding components and transmission lines. Precise alignment is crucial to maximize power transfer efficiency and reduce signal reflections in the system. Matching networks are crucial for establishing smooth connectivity between the LNA and its external surroundings. They help maintain a balanced signal flow and reduce impedance differences that may affect the amplifier's performance. The careful use of these networks is crucial in amplifier engineering, significantly enhancing the effectiveness and dependability of the LNA.

Matching networks in LNAs play a crucial role in improving power transfer and reducing signal reflections, which strengthens the amplifier's performance in a communication system. Intentional impedance matching is not just a technical detail but a fundamental approach for achieving the best amplifier performance. Engineers use exact matching networks to incorporate an LNA into its operational environment, resulting in an amplified signal with maximum quality and efficiency. Impedance matching is a crucial discipline in amplifier design that demonstrates a dedication to technical precision for optimal amplifier performance.

#### 1.2.8 Stability and Linearity

Stability is a crucial factor in Low Noise Amplifier (LNA) design to prevent unwanted oscillations or instabilities. Engineers use feedback networks and stabilize components to strengthen the LNA and ensure its reliable operation in the communication system. Ensuring stability is crucial in LNA engineering to prevent any negative impacts on the amplifier's dependability and performance.

The idea of linearity is crucial in LNA design, as it determines the amplifier's capacity to accurately replicate input signals without distorting them. This quality is especially important in situations where the LNA deals with strong interfering signals. Maintaining good linearity is crucial to prevent signal degradation and preserve signal integrity. Striving for excellent linearity in LNA design showcases a dedication to engineering precision. The amplifier's ability to faithfully replicate input signals, especially under difficult circumstances, highlights its importance as a crucial component in advanced communication systems.

#### 1.2.9 Power Consumption

In the complex field of Low Noise Amplifier (LNA) design, achieving low noise and high gain is crucial, but balancing power consumption is also important, especially in situations with limited energy resources like battery-powered devices. Balancing low noise, high gain, and power efficiency requires precise design strategies to optimize power consumption while maintaining important noise performance. It is crucial to maintain a careful balance in real LNA implementations to achieve high efficiency while ensuring optimal noise characteristics. This balance is necessary to overcome the problems given by energy limits in different applications.

A comprehensive comprehension of LNA basics goes beyond only focusing on low noise and high gain, encompassing a wide range of factors. This thorough analysis covers important factors like noise figure, bandwidth, transistor choice, and biasing, all of which have a unique impact on the performance of the LNA. Careful coordination of impedance matching, strategic stability control, and maintaining linearity are other complexities in this complicated design. The importance of power consumption is significant and requires a balanced approach to enhance energy efficiency while maintaining low noise and achieving substantial gain.

To master LNA design, one must combine these complex ideas. It requires a deep understanding of low noise, gain, noise figure, bandwidth, and the intricate relationship between transistor technology and biasing. Implementing impedance matching, ensuring stability, and maintaining linearity are important design considerations. This expertise goes beyond the usual limits to include a complex comprehension of power usage, recognizing its vital importance in contemporary, energy-efficient uses. Mastering these concepts enables engineers to customize LNAs precisely, guaranteeing their smooth incorporation into particular applications and reinforcing their position as strong performers in communication systems.

#### 1.3 Objective of the Thesis

The primary objectives of this thesis are:

- 1. To design Substrate Integrated Waveguide (SIW) Resonator for required resonance frequency.

- 2. To design a Low Noise Amplifier (LNA) for Ultra-Wide Band (UWB) wireless receiver using SIW Resonator.

- 3. To explore the performance of the proposed LNA

Through the pursuit of these objectives, this thesis endeavours to contribute to the advancement of UWB communication systems by providing an innovative approach to Ultra-Wide Band OP-AMP design using SIW resonators.

#### 1.4 Significance and Scope

The significance of this research lies in its pioneering approach to the design of a wideband (WB) low-noise amplifier (LNA) using substrate integrated waveguide (SIW) technology. Traditional CMOS LNA design often relies on active spiral inductors, presenting challenges in achieving a delicate balance between gain, noise performance, and frequency compatibility. This study

introduces an innovative inductor-less SIW-based LNA, representing a ground-breaking departure from conventional methodologies. The seamless integration of SIW resonators not only eliminates the need for active spiral inductors but also opens new dimensions in high-frequency electronics, setting a technological milestone in CMOS LNA design.

The proposed LNA, operating in the 67 GHz to 71.5 GHz frequency range, aligns strategically with the 180 nm technology transition frequency, showcasing its relevance in contemporary technological landscapes. The incorporation of a sophisticated noise canceller circuit further enhances noise reduction, maintaining exceptional input and output matches. This research's significance extends beyond the immediate context, contributing to the ongoing discourse in high-frequency electronics and establishing new avenues for future exploration and refinement in CMOS LNA design.

The scope of this study encompasses the comprehensive exploration and implementation of SIW resonators in the design of a high-performance WB LNA. By focusing on the frequency range of 67 GHz to 71.5 GHz, the research addresses the specific challenges and opportunities associated with the 180 nm technology transition frequency. The investigation includes a detailed analysis of the inductor-less LNA's performance, the integration of SIW resonators, and the impact of the noise canceller circuit on key parameters such as gain, noise figure, and power gain. The study's scope extends to the broader implications of SIW technology in CMOS LNA design, emphasizing its potential to revolutionize high-frequency electronic systems.

#### 1.5 Thesis Outline

Thesis is organized in five different chapters including this introduction chapter 1. In the introductory chapter of this thesis, we establish the foundation for a comprehensive study on the design and performance analysis of a CMOS amplifier tailored for ultra-wideband wireless receivers, with a specific focus on

the integration of a Substrate Integrated Waveguide (SIW) resonator. We outline the motivation behind this research, highlighting the significance of developing efficient amplifiers for improving wireless communication systems. Additionally, the chapter sets the stage for the subsequent analysis by presenting the objectives and scope of the study.

Chapter 2 delves into the fundamentals of Low-Noise Amplifiers (LNAs). It introduces readers to the essential concepts, operating principles, and key parameters governing the performance of LNAs. Additionally, a historical overview traces the evolution of LNA technology, providing a contextual foundation for the subsequent chapters.

A comprehensive overview of existing work in LNA design is presented in Chapter 3. The literature review summarizes relevant research, highlighting advancements, limitations, and emerging trends in LNA technology. By examining the current state of the field, this chapter provides a valuable context for the novel contributions of the present study.

Chapter 4 shifts focus to the design and optimization of Ultra-Wideband (UWB) LNAs. Readers are introduced to the unique characteristics of UWB LNAs and the design approach employed in this study. The chapter explores optimization techniques aimed at enhancing LNA performance, with a particular emphasis on the integration of Substrate Integrated Waveguide (SIW) technology.

The final chapter synthesizes the key findings of the research. It offers a concise summary of major contributions, discussing their implications and potential applications. Furthermore, the chapter outlines the scope for further research, identifying areas for exploration and refinement in the evolving field of LNA design.

### 2 Fundamentals of LNA

This chapter introduces the fundamental concept of S parameters, crucial for characterizing the behavior of two-port networks in RF circuits, with a particular focus on their application in optimizing Low Noise Amplifiers (LNAs) for wireless communication systems.

#### 2.1 S Parameters

Instead of Z, Y, ABCD, and H parameters, the S parameter is frequently used to define two port networks when both networks are operating at RF frequencies. In terms of waves that are incident and waves that are reflected, the S parameters are defined. As can be seen in Figure 2.1, The waves that are incident and reflected at port\_1 are denoted by  $x_1$  and  $y_1$ , respectively. Similarly, the waves that are incident and reflected at port\_2 are denoted by  $x_2$  and  $y_2$ , respectively.

Figure 2.1: Two-port Network

The  $y_1$  and  $y_2$  are dependent on the  $x_1$ ,  $x_2$  and the delineation of the relationship between incident and reflected waves is explicated through the utilization of equations (2.1) and (2.2).

$$y_1 = S_{11}x_1 + S_{12}x_2 \tag{2.1}$$

$$y_2 = S_{21}x_1 + S_{22}x_2 \tag{2.2}$$

Equations (2.1) and (2.2) provide clear comprehension of the S parameters. Specifically,  $S_{11}$  is characterized as follows:

$$S_{11} = \frac{y_1}{x_1} | at x_2 = 0 {(2.3)}$$

$S_{11}$  indicates the amount of  $x_1$  that is reflected back to  $y_1$ .  $S_{11}$  displays the input matching measurement for optimal power transfer. If the reflected power  $y_1$  is 0, it indicates that all input power has been transferred. The  $S_{11}$  value is either 0 or  $-\infty$  in logarithmic terms, indicating a perfect match. To achieve optimum power transfer, it is ideal for the practical value of  $S_{11}$  to be minimized, preferably below -10 dB. The term  $S_{12}$  is defined as

$$S_{12} = \frac{y_1}{x_2} \mid at \ x_1 = 0 \tag{2.4}$$

The magnitude of  $S_{12}$  indicates the extent of power transfer from port\_2 to port\_1. It quantifies the effectiveness of isolation between port\_1 and port\_2, with a lower value signifying superior isolation from port\_2 to port\_1. The definition of  $S_{21}$  is as follows:

$$S_{21} = \frac{y_2}{x_1} | at x_2 = 0 {(2.5)}$$

$S_{21}$  represents the ratio of power at port\_2 to power at port\_1, elucidating the power gain of the two-port network. Likewise, the definition of  $S_{22}$  is as follows:

$$S_{22} = \frac{y_2}{x_2} | at x_1 = 0 {(2.6)}$$

$S_{22}$  evaluates the matching of the output port. Minimize the value of  $S_{22}$  to improve port\_2 matching with the load and maximize power transfer to the load. An ideal amplifier should exhibit low values for  $S_{11}$ ,  $S_{22}$ , and  $S_{12}$ , while having a high value for  $S_{21}$ .  $S_{11}$  is utilized for assessing input match, while  $S_{21}$  is employed for measuring LNAs power gain.

Analysis of the stability of the two-port network is conducted utilizing S parameters. The stability (*K*) requirement is defined by the S parameters as (2.7).

$$K = \frac{1 - |S_{22}|^2 - |S_{11}|^2 + |\Delta_s|^2}{2|S_{12}S_{21}|} > 1$$

(2.7)

#### 2.2 Performance Matrices of LNA

Key performance metrics of the LNA include:

- ➤ Gain of Power and Impedance Alignment

- ➤ Noise Figure (NF)

- ➤ Electrical Power Utilization

- ➤ Linearity (IIP3)

- Stability

#### 2.2.1 Gain of Power and Impedance Alignment

The Low Noise Amplifier (LNA) is the initial amplification stage in a receiver designed to boost faint signals received from the antenna. To achieve maximum power transfer from the antenna's output to the LNA's input, the input impedance of the LNA must be matched to the output impedance of the antenna. When impedance is mismatched, signals are reflected back, causing noise. Input impedance matching is a crucial element in LNA design to optimize power transfer.  $S_{11}$  in the S-parameters of a two-port network represents the ratio of reflected signal power at port\_1 to the input signal power.  $S_{11}$  is measured in decibels (dB) and a value below – 10 dB is the ideal target. A – 10 dB,  $S_{11}$  value indicates that 10% of the total input power is reflected back. For optimal transfer of amplified output power from the Low-Noise Amplifier (LNA) to the next stage input, the output impedance of the LNA should be matched with the input impedance of the next stage. The measurement of output impedance matching is determined by the S-parameter  $S_{22}$ . Another important design performance parameter is Power gain  $(S_{21})$ , which should be maximized to enhance the amplitude of weak received signals.

#### 2.2.2 Noise Figure

The evaluation of the noise characteristics of a two-port network involves determining its Noise Factor (F). The Noise Factor represents the ratio of the total output noise power to the output noise originating from the input source. When expressed in dB, this Noise Factor is termed the Noise Figure (NF)

$$SNR = \frac{P_{signal}}{P_{noise}} \tag{2.8}$$

$$F = \frac{\frac{P_{s\_in}}{P_{n\_in}}}{\frac{P_{s\_out}}{P_{n\_out}}}$$

(2.9)

$$NF = 10 \log(F) \tag{2.10}$$

Where, SNR = Signal to Noise Ratio,  $P_{signal} = Signal$  power,  $P_{noise} = Noise$  power  $P_{s\_in} = input$  signal power,  $P_{n\_in} = the$  input noise power,  $P_{s\_out} = output$  signal power and  $P_{n\_out} = output$  noise power.

In electronic circuits, noise is a stochastic and non-deterministic variable. The presence of circuit noise is attributed to the characteristics of the materials utilized or external interferences. Noise causes signal degradation. It is necessary to thoroughly study and devise methods to limit the impact of noise on signals. The next section describes the primary sources of noise in the circuit [4], [5].

Thermal noise in circuits arises from the stochastic movement of electrons. The power (*P*) of the thermal noise signal is represented by equation (2.11).

$$P = KT\Delta f \tag{2.11}$$

Here, K denotes Boltzmann's constant,  $\Delta f$  is the system's bandwidth in Hz, and T represents the temperature in Kelvin. The model provided in equation (2.12) depicts the thermal noise voltage  $(\overline{V_{th}^2})$  generated within a resistor.

$$\overline{V_{th}^2} = 4KRT\Delta f \tag{2.12}$$

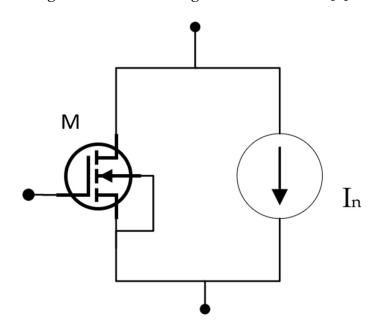

MOSFETs also display thermal noise caused by the movement of carriers in the channel. The noise is represented by incorporating a current source in parallel with a MOSFET that has a conducting channel, as illustrated in Figure

2.2. This noise current  $(\overline{I_n^2})$  is represented by equation (2.13) when the device operates in triode mode [6].

$$\overline{I_n^2} = 4KT\gamma g_{d0}\Delta f \tag{2.13}$$

In this context,  $\gamma$  represents the excess noise parameter, and  $g_{d0}$  is the drain-to-source conductance when  $V_{DS}$  equals 0. When a MOSFET is in saturation mode, the thermal noise current in the channel is modeled as illustrated in equation (2.14) [7].

$$\overline{I_n^2} = 4KT\gamma g_m \Delta f \tag{2.14}$$

Where,  $\gamma = \frac{2}{3}$  [8] for long channel device, for short-channel and submicron MOSFETS,  $\gamma$  has higher values, in a range between 1 and 3 [9].

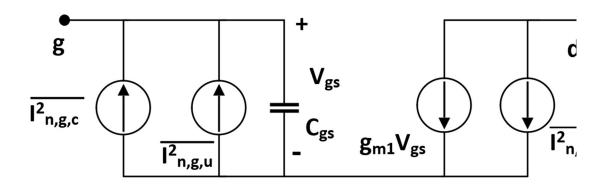

Figure 2.2: MOSFET channel thermal noise representation [7]

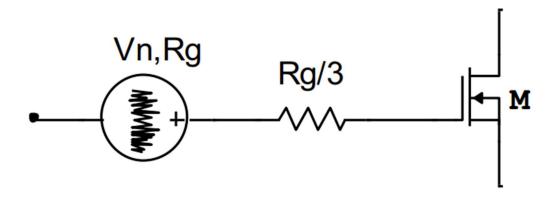

Thermal noise caused by dispersed gate resistance is another form of noise in MOSFETs. The gate resistance varies according to the MOSFET's geometry. Equation (2.15) represents the resistance of a single polysilicon gate finger ( $R_G$ ) that is interconnected on both sides [10].

$$R_G = \frac{1}{12} \rho_{sh} \frac{W}{L} + \frac{\rho_{con}}{WL}$$

(2.15)

Where,  $\rho_{sh}$  is silicide sheet resistance, W and L is the width and length of the MOSFET channel and  $\rho_{con}$  is silicide to polysilicon contact resistance.

Figure 2.3: Equivalent noise model for gate resistance [5]

Figure 2.3 illustrates the equivalent noise model of a gate resistor, with  $\frac{R_g}{3}$  representing the equivalent gate resistance and  $V_n$ ,  $R_g$  representing the equivalent gate noise voltage [5], [11]. Enhancing silicide sheet resistance can be achieved through the use of a multi-finger gate design [10], [12], resulting in a reduction of gate resistance thermal noise. Should the power spectral density of the noise be notably lower than that of the channel thermal noise, it may be deemed inconsequential.

$$4KT\frac{R_G}{3} \ll \frac{4KT\gamma}{g_m} \tag{2.16}$$

The flicker noise in MOSFET is caused by a physical phenomenon and is characterized by its unpredictability. It encompasses the interaction between the silicon substrate (Si) and the gate oxide (SiO<sub>2</sub>). Flicker noise emanates from the stochastic fluctuations in charge carriers within the channel, originating from the capture and emission processes of carriers at the silicon-silicon dioxide interface. Flicker noise decreases as frequency increases, making it insignificant at higher frequencies. Within the model, there exists a flicker noise voltage generator connected in series with the gate. The representation of this flicker noise ( $\overline{V_{nf}^2}$ ) is articulated by equation (2.17).

$$\overline{V_{nf}^2} = \frac{Kf}{C_{ox}WLf} \tag{2.17}$$

Here, Kf denotes a process-dependent constant, while  $C_{ox}$ , W, and L represent the gate oxide capacitance per unit area, width, and length of the MOSFET, respectively. Notably, for p-channel devices, Kf exhibits a lower value compared to n-channel devices, leading to reduced flicker noise in PMOS transistors.

Shot noise arises from current fluctuations across a p-n junction potential barrier. Charge carriers diffuse randomly, resulting in varying speeds among carriers. The shot noise is defined as (2.18).

$$\overline{I_{ns}^2} = 2qI_{DC} \tag{2.18}$$

Shot noise results from the fluctuations in current around its mean value, with q representing the electron charge and  $I_{DC}$  denoting the direct current. Shot noise is more pronounced in bipolar junction transistors than in MOSFETs due to the fact that both emitter and collector currents contribute to the generation of shot noise. DC gate leakage current in MOSFETs generates shot noise but is often minimal and can often be disregarded.

#### 2.2.3 Electrical Power Utilization

Efficient power management is an essential design consideration for products relying on battery power. A low power dissipation design not only extends battery life but also reduces cooling system costs and enables increasing chip complexity to integrate more functionality.

#### 2.2.4 Linearity

In the design of LNAs, considering linearity is crucial, particularly when handling weak input signals and strong interference signals. Insufficient linearity in a system can led to cross modulation caused by powerful interference signals, resulting in unwanted intermodulation distortion.

The input-output relationship for a memoryless linear system is stated as equation (2.19).

$$y(t) = ax(t) (2.19)$$

For a time-variant system, the function a is dependent on time, whereas for a time-invariant system, the function a remains constant. The input/output relationship of a memoryless nonlinear system is defined as equation (2.20) [13].

$$y(t) = a_0 + a_1 x(t) + a_2 x^2(t) + a_3 x^3(t) + \dots$$

(2.20)

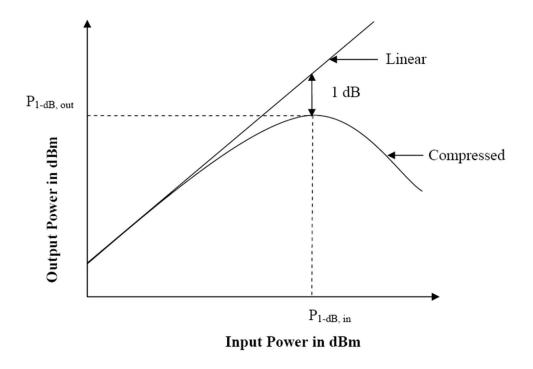

The calculation of harmonics indicates that the gain experienced by Acos(wt) is expressed as  $\left(\alpha_1 + \frac{3\alpha_3A^2}{4}\right)$ , showcasing significant variations with increasing A. In instances where  $\alpha_3 < 0$ , resulting in a reduction in gain with an increase in A, this effect is quantifiable through the 1dB Gain compression point. This point denotes the input power level at which a signal induces a 1dB reduction in gain from its extrapolated value, as delineated in Figure 2.4. When presented on a logarithmic scale, the output power at a 1dB compression point deviates by 1dB from its ideal value relative to input power [13].

Figure 2.4: 1 dB compression point [13]

The computation of the 1 dB compression points entails establishing equivalence between the compressed gain and a value 1 dB lower than the ideal gain.

$$20 \log \left( \alpha_1 + \frac{3\alpha_3 A^2}{4} \right) = 20 \log(\alpha_1) - 1 dB \tag{2.21}$$

A 1 dB compression signifies a 10% decrease in gain and is commonly employed to describe RF systems. Another negative consequence of compression arises when a powerful interfering signal is present alongside the received signal. In the time domain, the faint target signal is overlaid over the powerful interfering signal. As a result, the receiver's gain is diminished by the significant interference caused by the interferer, even if the desired signal is weak, a phenomenon known as "desensitization." This phenomenon diminishes the signal-to-noise ratio (SNR) at the output, a critical aspect even when the signal lacks amplitude information [13].

For a qualitative assessment of desensitization, consider  $A_1 \cos(\omega_1 t)$  as the desired signal and  $A_1 \cos(\omega_1 t)$  is desire signal and  $A_2 \cos(\omega_2 t)$  as the interfering signal. The input to the amplifier is expressed as  $x(t) = A_1 \cos(\omega_1 t) + A_2 \cos(\omega_2 t)$ . The output of the nonlinear system manifests as –

$$y(t) = \left(\alpha_1 + \frac{3}{4}\alpha_3 A_1^2 + \frac{3}{2}\alpha_3 A_2^2\right) A_1 \cos \omega_1 t + \dots \dots$$

(2.22)

Therefore, the gain encountered by the desired signal is given by  $\left(\alpha_1 + \frac{3}{2}\alpha_3A_2^2\right)$ , a diminishing function of  $A_2$  when  $\alpha_1\alpha_3 < 0$ . An increase in the value of  $A_2$  leads to a reduction in gain, eventually reaching zero. This circumstance is termed signal blocking. In RF design, the term "blocking signal" or "blocker" denotes interferers that desensitize a circuit, even without reducing the gain to zero [13].

#### 2.2.5 Stability

The design of the MOSFET amplifier with high-power gain has been meticulously crafted to guarantee stability amidst changing input and output loading conditions. The stability factor K, derived from S parameters, is a

common metric used to analyze stability characteristics, as defined by equation (2.23).

$$K = \frac{1 + |\Delta|^2 - |S_{11}|^2 - |S_{22}|^2}{2|S_{21}||S_{12}|}$$

(2.23)

Where,  $\Delta = S_{11}S_{22} - S_{21}S_{12}$ , determinant of S parameter matrix. Value of K greater than unity and  $\Delta$  less than unity make system unconditionally stable.

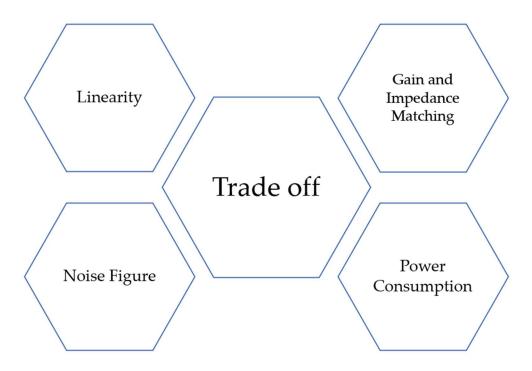

Amplifiers with high power gain ( $S_{21}$ ) need the feedback parameter ( $S_{12}$ ) to be minimal according to the expression for K. The cascode amplifier circuit enhances stability by decreasing the gain at the output of the driver transistor, resulting in a more unilateral device. The design of an LNA involves a multi-dimensional optimization issue. Trade-offs arise from the fact that optimizing individual specifications does not result in uniform sizing or biasing solutions. This underscores the necessity for designers to meticulously choose the optimal performance criteria tailored to the intended use of the LNA.

In conclusion, S parameters serve as indispensable tools for evaluating and refining the performance of RF circuits, notably LNAs, by enabling precise assessment of parameters such as impedance matching, power gain, and stability, thus facilitating the design of efficient and robust wireless communication systems.

## 3 Literature Review

This literature review chapter provides a comprehensive analysis of existing research pertaining to the design and performance analysis of CMOS amplifiers tailored for ultra-wideband wireless receivers, with a specific focus on the integration of Substrate Integrated Waveguide (SIW) resonators. It aims to examine the current state of knowledge in this field, identify key research trends, and establish a foundation for the subsequent investigation presented in this thesis.

#### 3.1 Wideband LNA Implementation Approaches

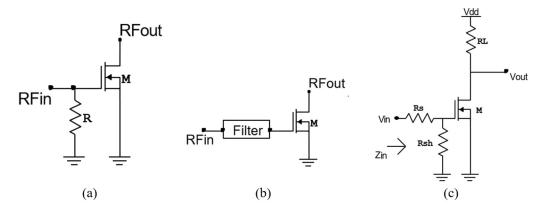

Three alternative ways can be used to implement a multi-standard LNA. Utilizing separate narrowband LNAs for each communication standard is a straightforward method that is easy to construct and delivers exceptional results. However, the power consumption and silicon space needed for several LNAs might be significant. Using a multiband/band switching LNA. Multiband technology is more power-efficient than narrow band LNAs but necessitates a greater area due to the utilization of bigger tuning inductors [14] – [19]. The third way utilizes a single wideband LNA to process all standards simultaneously. The broadband LNA is more cost-effective and space-efficient than the first and second techniques, but it has a downside of having a modest power gain [20] – [27]. A broadband LNA may effectively support many standards [28]. Wideband LNAs provide consistent gain, input impedance matching, noise figure (NF), and third-order input intercept point (IIP3) across their whole frequency range.

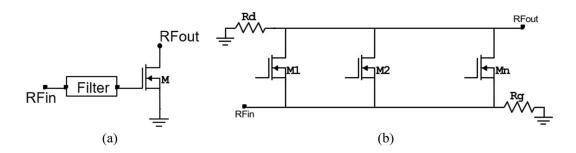

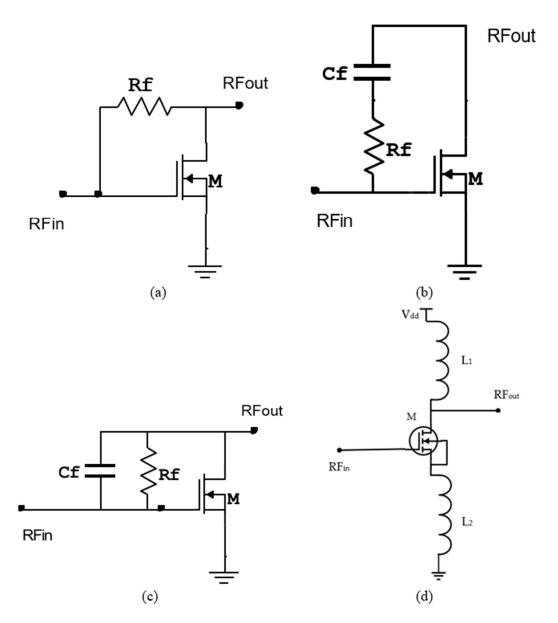

Figure 3.1: (a) Resistive termination, (b) Common gate, (c) Feedback LNA topology [14]

Various topologies utilized in literature for wideband input matching include resistive termination common source, common gate, feedback, CS with wideband input filter, and distributed, as seen in Fig. 3.1 and Fig. 3.2.

Figure 3.2: (a) Filter, (b) Distributed LNA topology [15]

## 3.2 Common Source with Resistive Termination LNA Topology

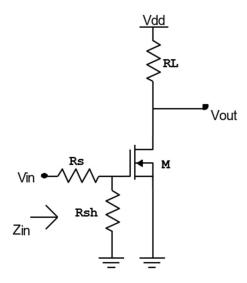

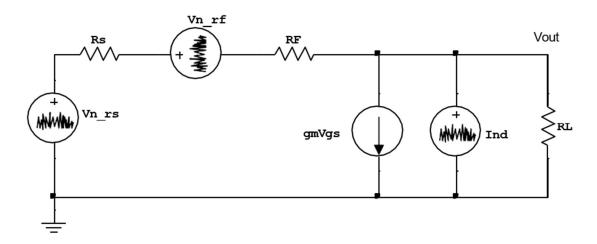

Figure 3.3: Common Source (CS) with resistive termination topology [16]

To achieve wideband input impedance matching, one way is to add a shunt resistor at the input of the CS LNA, as seen in Figure 3.3.

Voltage gain of resistive termination is expressed as

$$A = -g_m R_L \left(\frac{R_{sh}}{R_s + R_{sh}}\right) \tag{3.1}$$

Where,  $R_{sh}$  = shunt resistance,  $R_s$  = series resistance and  $R_L$  = load resistance. For  $R_{sh}$  =  $R_s$  voltage gain is simplified as –

$$A = -g_m \left(\frac{R_L}{2}\right) \tag{3.2}$$

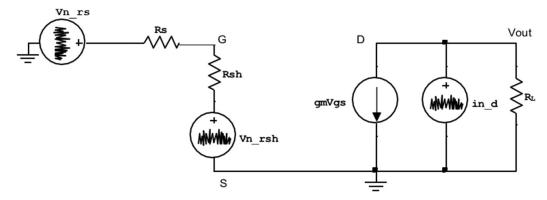

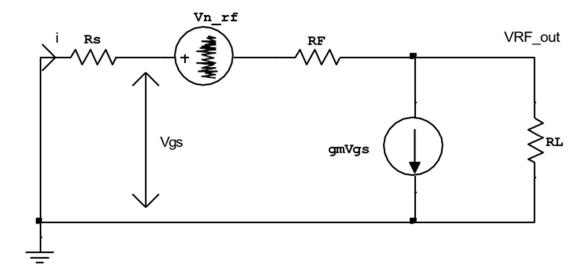

Figure 3.4: AC equivalent circuit with noise sources of resistive termination CS

The resistive termination gain at input matching is half of the Common source gain  $(-g_m R_L)$  as demonstrated in equation (3.2). Noise figure is a measure of the degradation of the signal-to-noise ratio by a device or system.

$$F = \frac{Total\ output\ noise\ power}{Output\ noise\ due\ to\ input\ source} \tag{3.2}$$

Total noise figure of this topology can be expressed as

$$NF = 2 + \frac{4\Upsilon}{g_m R_s} \tag{3.3}$$

Where,  $\Upsilon$  is a noise parameter and  $R_{sh}=R_s$  is shunt resistor value. Limitations of this topology are:

- ✓ Poor noise figure

- ✓ Input signal is dampened by a voltage divider, resulting in a reduction of gain.

- ✓  $R_{sh}$  adds extra thermal noise.

- ✓ To accommodate the additional shunt inductor at higher frequencies, it is necessary to adjust the input capacitance  $C_{gs}$ .

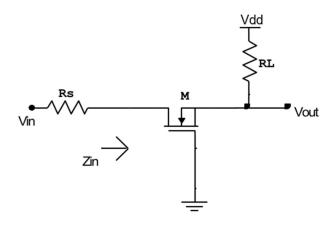

#### 3.3 Common Gate Topology

The Common Gate (CG) amplifier inherently presents extensive input matching capabilities. Equation (3.4) denotes the expression for the input impedance of the common gate configuration.

Figure 3.5: Common Gate (CG) topology [17]

$$Z_{in} = \frac{1}{g_m} \tag{3.4}$$

Where,  $Z_{in}$  is the input impedance and  $g_m$  is transconductance of the MOSFET

#### 3.3.1 Analysis Noise Figure of CG

The Common Gate (CG) topology encounters noise originating from two distinct sources: the source resistor and MOSFET channel noise. The Noise Figure (NF) of the Common Gate (CG) is formally represented by equation (3.5), when input impedance match  $R_s = \frac{1}{g_m}$ .

$$NF = 1 + \Upsilon + \frac{4R_s}{R_L} \tag{3.5}$$

The Noise Figure (NF) of a Common-Gate (CG) topology can be calculated using equation (3.5), where  $\Upsilon$  is the process-dependent noise parameter. Increasing the transconductance ( $g_m$ ) of a common gate (CG) configuration improves its Noise Figure but reduces its wideband input matching. The tradeoff involves setting the ( $g_m$ ) value to achieve both low noise figure and wideband matching. To decrease the impact of Miller capacitance in a common gate (CG) configuration, one can utilize a cascode structure with a common source (CS).

The input impedance of a common gate with common source cascode structure is represented by equation (3.6).

$$Z_{in} = \frac{1}{g_m + g_{mb}} \tag{3.6}$$

Where  $g_m$  and  $g_{mb}$  represent the transconductance of the transistors. The main disadvantages of the CG architecture include poor gain, increased Noise Figure (NF) with wideband matching, and high-power consumption [29], [30].

Various hybrid topologies with conjugate matching were employed in literature to achieve broad frequency coverage, low noise figure, and high-power amplification [14, 17, 31]. Positive feedback in the common gate configuration relaxes the constraint on selecting transconductance  $(g_m)$  for input matching. Positive feed-back increases loop gains and decreases overdrive voltage, leading

to a degradation in linearity and noise figure performance [32]. The feedback circuit intentionally utilizes an inverted amplifier to improve transconductance. Negative feedback in the control group decreases noise figure and power usage, but it has compromised the stability of the design. The positive-negative feedback gain-boosted design technique provides enhanced noise figure and amplification without compromising linearity and input impedance matching. It has yielded equivalent power enhancement to positive feedback while utilizing only half the electricity. Different methods including dual negative feedback and noise cancellation are employed with common gate to enhance the performance of the Low-Noise Amplifier.

The paper [33] utilized parallel common source with CG to balance the tradeoff between input impedance matching and noise figure of the CG amplifier. Various distortion cancellation approaches are utilized with the CG to enhance linearity [21, 34, 35, 26].

### 3.4 Feedback LNA Topologies

Utilizing negative feedback in low-noise amplifiers is a common method to provide broad input impedance matching while maintaining low noise figure. Several unfavorable feedback LNA configurations are displayed in Figure 3.6. Using a lossless transformer as feedback provides optimal performance but necessitates a bigger silicon area [36]. Resistors in the feedback network, such as series RC, parallel RC, and transistors, are frequently employed. The utilization of negative feedback architecture contributes to the improvement of the noise figure and input impedance matching of the device.

Figure 3.6: Feedback topologies a) resistive b) series RC c) parallel RC and d) transformer

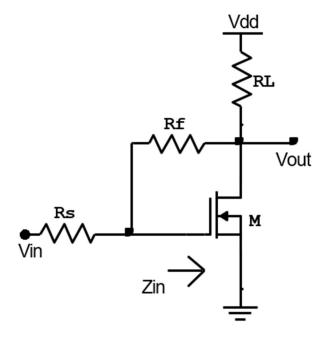

## 3.4.1 Resistive Feedback LNA Topology

Figure 3.7: Resistive feedback common source (CS) topology

#### 3.4.1.1 Gain Analysis

Resistive feedback amplification the topology of a CS can be determined from its AC equivalent circuit, illustrated in figure 3.8.

Figure 3.8: AC equivalent circuit of resistive feedback CS topology

Using Kirchhoff's Current Law in the input loop results in the relationship between input and output voltages.

$$V_{in} = i_{in}(R_s + R_f) + V_{out}$$

(3.7)

$$V_{out} = (i_{in} - g_m V_{gs}) R_L \tag{3.8}$$

$$V_{gs} = \left(i_{in}R_f + V_{out}\right) \tag{3.9}$$

Where,  $R_s$ ,  $R_f$  and  $R_L$  are source, feedback, and load resistor, respectively. If  $R_f \gg R_c \& g_m R_f \gg 1$  then gain equation can be simplify as

$$A_{V,tot} = \frac{-g_m R_L}{R_S + R_f + R_L + g_m R_S R_L} \cong -g_m R_L \tag{3.10}$$

The input impedance of a resistive feedback common source amplifier is represented by equation (3.11).

$$Z_{in} = \frac{R_f + R_L}{1 + g_m R_L} \tag{3.11}$$

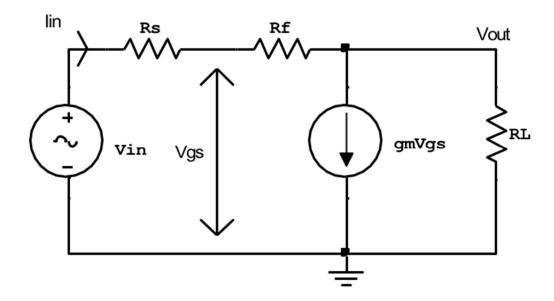

#### 3.4.1.2 Noise Figure Analysis

A resistive feedback amplifier experiences noise from three sources: source resistor, feedback resistor, and MOSFET. Total noise is the cumulative sum of all separate source noises.

Figure 3.9: AC equivalent circuit with noise sources of resistive feedback CS [37]

To determine the output noise caused by the feedback resistor, isolate the feedback resistance noise source and set all other sources in Figure 3.9 to zero.

Figure 3.10: Feedback resistance noise of resistive feedback CS [38]

Total noise figure is.

$$NF = 1 + \frac{\overline{V_{n,RF}}^2 \left[ \frac{R_L}{R_f} (1 + g_m R_s) \right]^2}{A_V^2 \overline{V_{n,RS}}^2} + \frac{\overline{I_{nd}}^2 R_L^2}{\overline{V_{n,RS}}^2 A_V^2}$$

(3.12)

$$NF = 1 + \frac{R_S}{R_f} \left( 1 + \frac{1}{g_m R_S} \right)^2 + \frac{\Upsilon}{g_m R_S}$$

(3.13)

Equation (3.13) demonstrates that the noise figure of resistive feedback is inversely proportional to  $R_f$  and  $g_m R_s$ . Increasing the feedback resistance value NF improves the design but worsens input impedance matching. A trade-off exists between noise figure and input matching in resistive feedback topology. A gate inductor is required in a resistive feedback CS amplifier at higher frequencies to eliminate the effect of  $C_{gs}$  and enhance gain.

Increasing the amount of the feedback resistor improves noise figure but negatively impacts linearity, input matching, and flat gain performance. The current inverter structure utilizes resistive feedback with NMOS/PMOS pair to enhance linearity, as discussed in references [37], [38]. This topology has a limitation of low bandwidth and utilizes an additional transistor for feedforward noise suppression, leading to increased power dissipation. Resistive feedback topologies in references [25], [39], [40] are utilized to produce improved

wideband performance using noise and distortion cancellation methods. The studies utilized resistive feedback with NMOS/PMOS pair in a cross-coupled manner for noise cancellation as referenced in [41], [42]. The design attained a remarkably low noise figure of 1.43 dB. To enhance noise figure in the design, large-size transistors were utilized, leading to a degradation in high-frequency response caused by the rise in parasitic capacitance.

Parasitic capacitance in resistive feedback circuits impairs the higher frequency response. Reactive feedback in literature enhances higher frequency response but necessitates a larger silicon surface.

#### 3.4.2 Reactive Feedback LNA Topology

Reactive feedback can be achieved by using a series RC, parallel RC, or series RLC circuit as a feedback network. The LNA [43] utilized series RC feedback with series and shunt inductive peaking to enhance bandwidth, noise figure, and gain flatness. However, this device lacks linearity.

The systems [44] – [48] utilize parallel RC feedback, depicted in Fig. 3.6 (c), to provide broadband operation (3.1–10.6 GHz) and enhanced noise figure. However, these devices also exhibit poor linearity.

The architecture [49] utilized series RLC feedback for wideband operation spanning from 3.1 to 10.6 GHz. This system utilizes positive and negative feedback to achieve low noise figure and enhance input matching, albeit at the expense of increased power consumption.

Figure 3.6 (d) illustrates the transformer feedback Low-Noise Amplifier (LNA) topology [50] – [52]. The LNA [52] utilized transformer feedback and current reuse to attain low noise figure and low power usage. This design has a drawback of needing a bigger silicon area and exhibiting poor linearity.

#### 3.4.3 Active Feedback LNA

The active feedback circuit consists of a common source amplifier in the input stage and a common drain amplifier in the feedback stage [53]. The

transconductance of the common drain stage determines the input impedance, whereas the transconductance of the common source amplifier affects the gain and noise figure of the entire Low-Noise Amplifier (LNA). Active feedback provides an additional level of control to adjust input impedance and noise figure apart from the design. The primary drawback of this architecture is the increased power consumption caused by the addition of the feedback step.

#### 3.5 Distributed Amplifier LNA Topology

Distributed amplifiers are commonly utilized in the construction of wideband low-noise amplifiers [54]. The many phases of a typical common-source distributed amplifier design use increased power and necessitate a bigger silicon footprint. Wideband frequency response is attained by creating transmission lines by the combination of the parasitic capacitances of transistors with inductors. Distribution amplifiers often have consistent amplification, strong linearity, and naturally low noise figure [29], [20], [55].