# Hardware-Software Codesign of Electrooculogram Signal Processors

# By Diba Das

(ID: 19MEE002P)

A thesis submitted in partial fulfillment of the requirements for the degree of MASTER of SCIENCE in Electrical and Electronic Engineering

Department of Electrical and Electronic Engineering

CHITTAGONG UNIVERSITY OF ENGINEERING AND TECHNOLOGY

# **Copyright Declaration**

I hereby declare that I am the sole author of the thesis titled "Hardware-Software Codesign of Electrooculogram Signal Processors". Along with this, submitted a softcopy is true copy of my final hardcopy thesis including any required final revisions, as accepted by the board of examination. I hereby release my copyright to Chittagong University of Engineering and Technology (CUET) for uploading the electronic version of the same to the 'Digital Repository (Institutional Repository)' of CUET after one year from the day of submission. Apart from this, the existing or to be approved Open Education Resources (OER) policies and procedures of Chittagong University of Engineering and Technology (CUET) shall be applicable to this research work. I also acknowledge my sincere delivering of copyright to Chittagong University of engineering and Technology (CUET) to reproduce this thesis by reprography or by other means, in total or by part at the necessity of individuals for the purpose of scholarly research.

Diba Das

19MEE002P

Department of Electrical and Electronic Engineering

Chittagong University of Engineering & Technology (CUET)

# **Dedication**

To my family members for their continuous support

## **List of Publications**

#### Journal Article

- Publication 1: Diba Das, Aditta Chowdhury, Abdurrashid Ibrahim Sanka, Ray C. C. Cheung, Quazi Delwar Hossain, and Mehdi Hasan Chowdhury, "Electrooculogram Based Point of Care Systems: A Systematic Review", SN Computer Science. (Under review)

- Publication 2: Diba Das, Mehdi Hasan Chowdhury, Aditta Chowdhury, Kamrul Hasan, Quazi Delwar Hossain, and Ray C. C. Cheung, "Application Specific EOG Processor for Blink Detection", Journal of Low Power Electronics and Applications. (Under review)

- Publication 3: Diba Das, Aditta Chowdhury, Ray C. C. Cheung, Quazi Delwar Hossain, and Mehdi Hasan Chowdhury, "EOG Signal Processor: A Multiclass Classifier to Detect Eye Movements", Journal of Signal Processing Systems. (Under review)

#### Conference

• **Diba Das**, Aditta Chowdhury, Abdurrashid Ibrahim Sanka, and Mehdi Hasan Chowdhury, "Design and Performance Evaluation of an FPGA based EOG Signal Preprocessor," 2023 International Conference on Electrical, Computer and Communication Engineering (ECCE), Chittagong, Bangladesh, 2023, pp. 1-6. **(Published)**

# Approval by the Supervisor

This is to certify that Diba Das has carried out this work under my supervision and that she has fulfilled relevant Academic Ordinance of the Chittagong University of Engineering and Technology, so that she is qualified to submit the following thesis in application for the degree of MASTER of SCIENCE in Electrical and Electronic Engineering

Dr. Mahdi Hasan Chayydhuwy

Dr. Mehdi Hasan Chowdhury

**Associate Professor**

Department of Electrical and Electronic Engineering Chittagong University of Engineering & Technology (CUET)

# Acknowledgement

First of all, I would like to express my sincerest gratitude to my supervisor, Dr. Mehdi Hasan Chowdhury, for his continuous mentorship and endless support in every step of my thesis. His insights and knowledge with humble research approach helped to complete my thesis. Dr. Mehdi always inspires me to achieve more and think differently in every aspect of life.

I would like to thank Dr. Ray C.C. Cheung, Associate Provost (Digital Learning), Professor of Computer Engineering, City University of Hong Kong, and Dr. Abdurrashid Ibrahim Sanka, Postdoctoral Research Fellow, City University of Hong Kong for helping to work in collaboration at CityU Architecture Lab for Arithmetic and Security (CALAS).

Also, I would like to thank Dr. Quazi Delwar Hossain, Professor, Department of EEE, and Aditta Chowdhury, Lecturer, Department of EEE, for their significant support and insights that helped me to complete my research work and write my thesis. My heartfelt gratitude goes to the examination committee members for their time and patience. I am forever grateful to all the members of the Department of Electrical and Electronic Engineering for their continuous support.

I want to thank my beloved parents for supporting me during my difficulties. I am grateful to all of my family members.

Finally, I want to express my humble gratitude to the almighty God for the knowledge he bestowed upon me and gave me the strength and peace of mind to complete this research work.

## **Abstract**

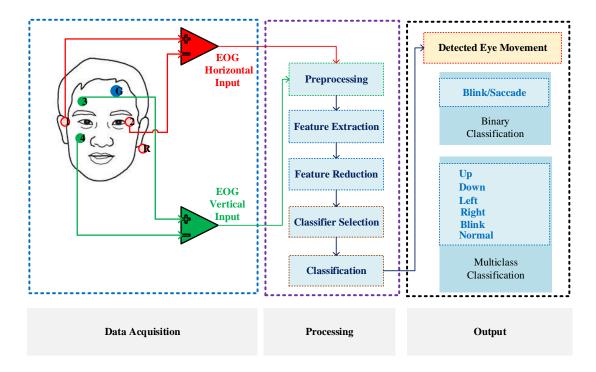

Electrooculogram (EOG) is a bioelectric signal carrying eye movement information. This signal can be utilized in medical and bio-electrical applications such as diagnosing different ocular diseases and controlling human-computer interfaces. Point of care (POC) systems refer to the systems where testing is performed right where the patient is. POC systems dedicated to detecting various eye conditions can be developed by hardware implementations of EOG. Field Programmable Gate Arrays (FPGAs) are reconfigurable integrated circuits offering flexible software features with fast parallel computation. Application specific designs in FPGA fix the functionality and reduce the number of components used providing cost-effectiveness, and power efficiency. In this research, a systematic investigation of the research trend on hardware implementations of EOG is presented first. After that, an in-depth analysis of two novel FPGA-based architectures is presented. The first work aims to design a hardware-optimized binary EOG processor for blink detection by using multichannel EOG signals containing horizontal and vertical EOG signals. After preprocessing the EOG signals, by extracting only two features- root mean square (RMS) and standard deviation (STD), blink and saccades are classified employing support vector machine (SVM) with 97.5% accuracy. The implemented system of this design in Xilinx Zynq-7000 FPGA achieves an accuracy of 95%. The second work aims to design a hardware-optimized machine learning based EOG signal processor to classify six different eye movements (up, down, normal, right, left, and blink) adopting an SVM classifier with average software accuracy of 97.92%. The accuracy of the implemented system in Zynq UltraScale+ is 95.56%. The efficacy of the developed systems is proved by comparing them with state-of-the-art technologies. A few potential future research scopes are mentioned at the end of the thesis.

### সারাংশ

ইলেক্ট্রোকুলোগ্রাম (EOG) সিগন্যাল হল একটি জৈব বৈদ্যুতিক (Bio-electric) সংকেত যা চোখের গতিবিধির তথ্য বহন করে। এই সিগন্যাল চিকিৎসা এবং জৈব বৈদ্যতিক অ্যাপ্লিকেশনে ব্যবহার করা যেতে পারে, যেমন চোখের বিভিন্ন রোগ নির্ণয় করা এবং মানব-কম্পিউটার পরিচালনা নিয়ন্ত্রণ করা। তাৎক্ষনিক সেবা কেন্দ্র (Point-of-Care System) রোগীর অবস্থানেই পরীক্ষা সম্পাদন করে। হার্ডওয়্যারে EOG সিগন্যাল বাস্তবায়ন করে তাৎক্ষনিক সেবা কেন্দ্র তৈরি করা সম্ভব, যা চোখের বিভিন্ন রোগ সনাক্তকরণের করতে সক্ষম। ফিল্ড প্রোগ্রামেবল গেট অ্যারে (FPGA) হলো পুনর্বিন্যাসযোগ্য ইন্টিগ্রেটেড সার্কিট যার অন্যতম বৈশিষ্ট্য দ্রুত গণনা। FPGA -এর মাধ্যমে নির্দিষ্ট কাজের জন্য ডিজিটাল সার্কিট ডিজাইনের মাধ্যমে প্রয়োজনীয় উপকরণের সংখ্যা কমানো যায়। এর ফলে, ব্যায় কমে, এবং শক্তি খরচ কম হয়। এই গবেষণায় সর্বপ্রথমে পূর্ববর্তী EOG এর হার্ডওয়্যার বাস্তবায়নের উপর একটি পদ্ধতিগত পর্যালোচনা ও বিশ্লেষণ করা হয়েছে। এরপর, FPGA-ভিত্তিক দুইটি পৃথক সিস্টেম ডিজাইন করা হয়েছে। প্রথম সিস্টেমের লক্ষ্য হলো EOG সিগন্যাল ব্যবহার করে চোখের পলক ফেলা সনাক্তকরণ। এই কাজে দুই চ্যানেল বিশিষ্ট EOG সিগন্যাল ব্যাবহার করে একটি হার্ডওয়্যার এর জন্য উপযোগী দুই শ্রেণীর EOG সিগন্যাল প্রসেসর ডিজাইন করা হয়েছে। মেশিন লার্নিং পদ্ধতি অনুসারে এই সিগন্যালকে প্রিপ্রসেসিং করার পর, দুইটি বৈশিষ্ট্য -রুট গড় বর্গক্ষেত্র (RMS) এবং স্ট্যান্ডার্ড ডেভিয়েশন (STD) নির্ণয়ের মাধ্যমে চোখের পলক ফেলা সনাক্তকরণ করা হয়েছে,। সাপোর্ট ভেক্টর মেশিন (SVM) এই কাজে ৯৭.৫% নির্ভুলতা অর্জন করে। FPGA Zynq-7000 বাস্তবায়িত এই ডিজাইনটি ৯৫% নির্ভুলতা অর্জন করে। দ্বিতীয় কাজের লক্ষ্য একটি হার্ডওয়্যার এর জন্য উপযোগী মেশিন লার্নিং ভিত্তিক EOG সিগন্যাল প্রসেসর ডিজাইন করা। এই কাজে চোখের ছয়টি ভিন্ন গতিবিধি (উপর, নিচে, স্বাভাবিক, ডান, বাম, এবং পলক ফেলা) SVM পদ্ধতিতে ৯৭.৯২% নির্ভুলতার সাথে শ্রেণীবিন্যাস করা সম্ভব হয়েছে। Zynq UltraScale+-এ বাস্তবায়িত এই ডিজাইনে ৯৫.৫৬% নির্ভূলতা অর্জন করা সম্ভব হয়েছে। অত্যাধুনিক প্রযুক্তির সাথে তুলনা করার মাধ্যমে এই গবেষণার কার্যকারিতা নির্ধারণ করা হয়েছে। থিসিসের শেষ অংশে কয়েকটি সম্ভাব্য ভবিষ্যত গবেষণা সম্বন্ধে সংক্ষিপ্ত আলোচনা করা হয়েছে।

# **Contents**

| Co         | opyri              | ght De  | claration                                     | i    |

|------------|--------------------|---------|-----------------------------------------------|------|

| D          | edica              | tion    |                                               | ii   |

| Li         | st of <sub>]</sub> | publica | tion                                          | iii  |

| Aj         | pprov              | al by t | he Supervisor                                 | iv   |

| A          | cknov              | wledge  | ment                                          | v    |

| <b>A</b> l | bstra              | ct      |                                               | viii |

| Ta         | ıble o             | f Cont  | ents                                          | x    |

| Li         | st of              | Figure  | S                                             | xi   |

| Li         | st of              | Tables  |                                               | xiii |

| N          | omen               | clature | 2                                             | xv   |

| 1          | Intr               | oducti  | on                                            | 1    |

|            | 1.1                | Backg   | ground                                        | 1    |

|            |                    | 1.1.1   | Electrooculogram                              | 3    |

|            |                    | 1.1.2   | Reconfigurable Computation Architecture- FPGA | 7    |

|            |                    | 1.1.3   | Module Selection                              | 9    |

|            |                    | 1.1.4   | Design Tool Selection                         | 10   |

|            | 1.2                | Prese   | nt State of the Problem                       | 12   |

|            | 1.3                | Specif  | fic Objectives                                | 13   |

|            | 1.4                | Contr   | ribution of the Work                          | 14   |

|            | 1.5                | Thesis  | s Outline                                     | 14   |

| 2 | Syst | tematic Review                             | 17 |

|---|------|--------------------------------------------|----|

|   | 2.1  | Electrooculogram Applications in Real-Life | 17 |

|   | 2.2  | Electrooculogram Point-of-care Systems     | 18 |

|   | 2.3  | Methodology of Systematic Review           | 19 |

|   |      | 2.3.1 Primary Phase                        | 19 |

|   |      | 2.3.2 Secondary Phase                      | 21 |

|   |      | 2.3.3 Research Findings                    | 21 |

|   | 2.4  | Detection Approaches                       | 22 |

|   | 2.5  | Hardware Implementations of EOG            | 23 |

|   |      | 2.5.1 FPGA based EOG Implementations       | 24 |

|   |      | 2.5.2 Other implementations of EOG         | 28 |

|   | 2.6  | State-of-the-Art                           | 28 |

|   | 2.7  | Summary                                    | 36 |

| 3 | Soft | tware Backend                              | 37 |

|   | 3.1  | Background                                 | 37 |

|   | 3.2  | Methodology                                | 39 |

|   | 3.3  | Datasets                                   | 41 |

|   | 3.4  | Preprocessing                              | 42 |

|   | 3.5  | Feature Extraction                         | 44 |

|   | 3.6  | Feature Reduction                          | 48 |

|   | 3.7  | Classification                             | 49 |

|   |      | 3.7.1 Binary Classification                | 52 |

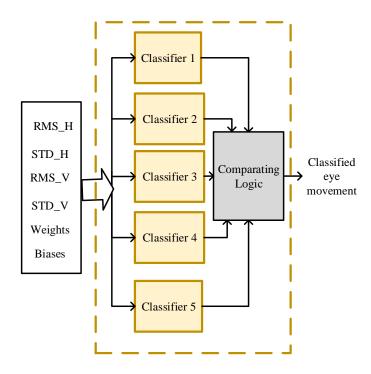

|   |      | 3.7.2 Multiclass Classification            | 53 |

|   | 3.8  | Summary                                    | 56 |

| 4 | Har  | dware Frontend                             | 57 |

|   | 4.1  | Background                                 | 57 |

|   | 4.2  | Processing Approaches                      | 59 |

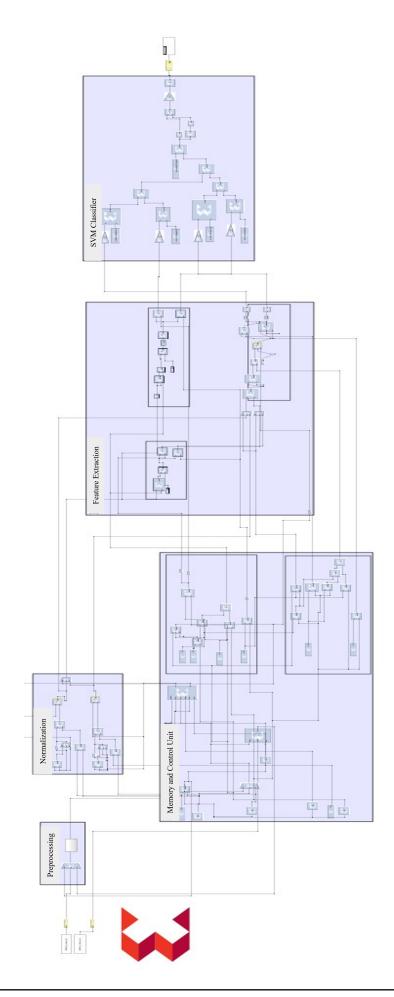

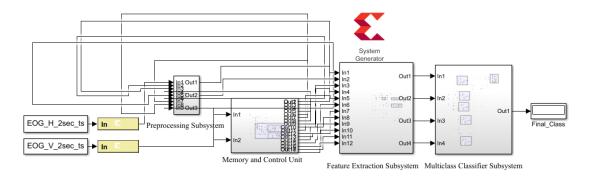

|   | 4.3  | Methodology                                | 60 |

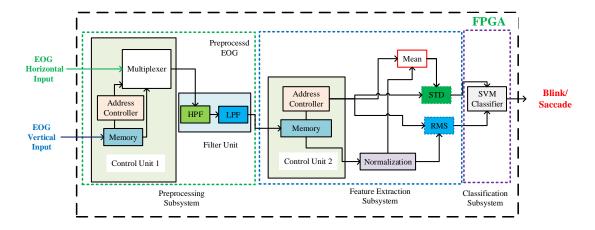

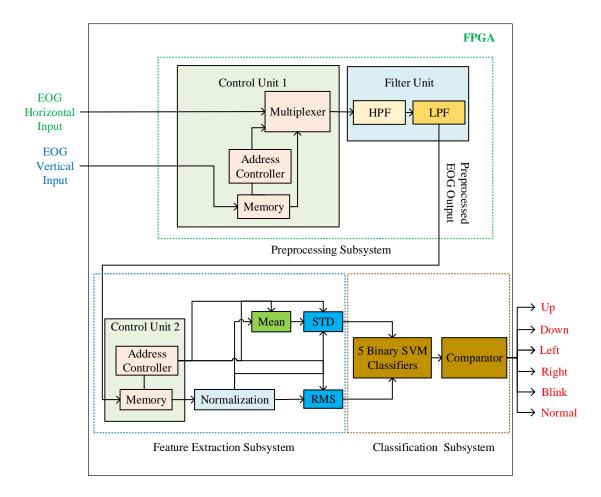

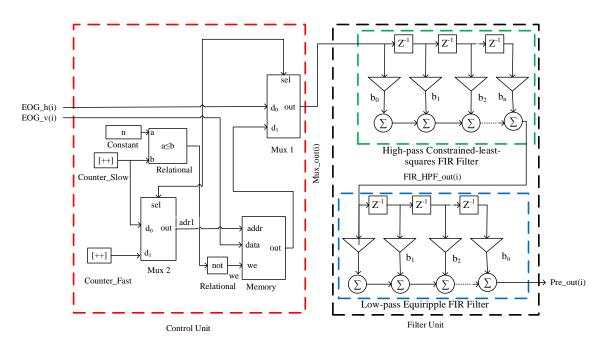

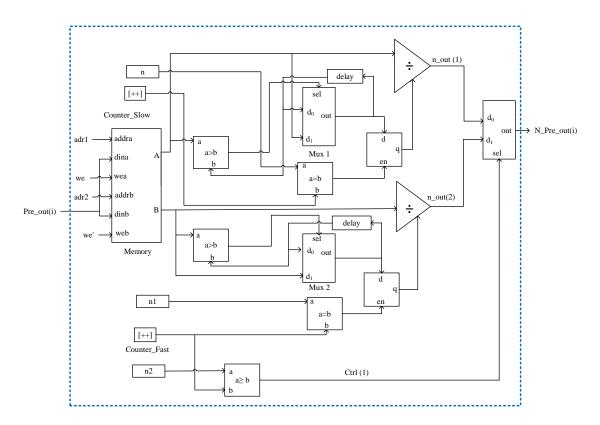

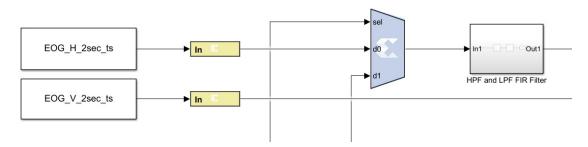

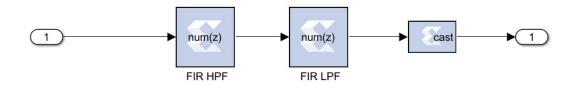

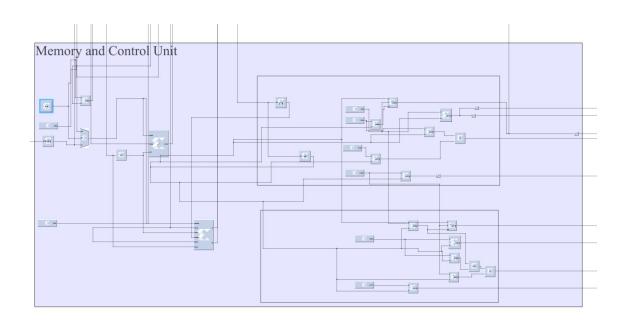

|   |      | 4.3.1 Preprocessing Subsystem              | 64 |

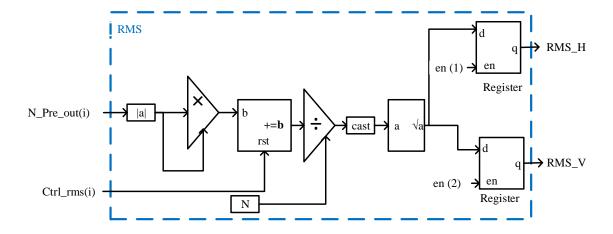

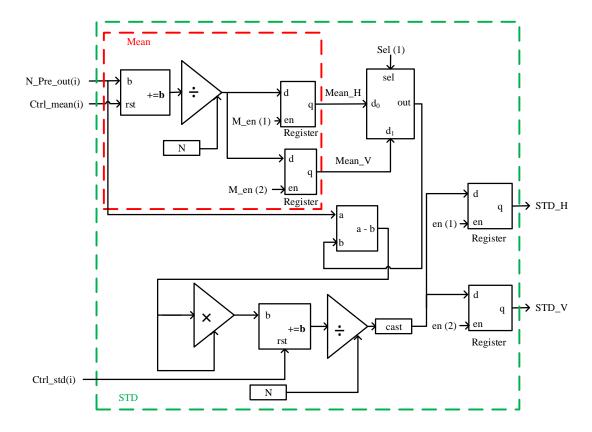

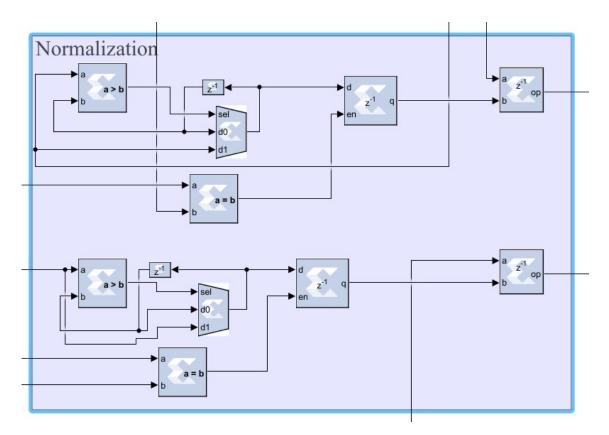

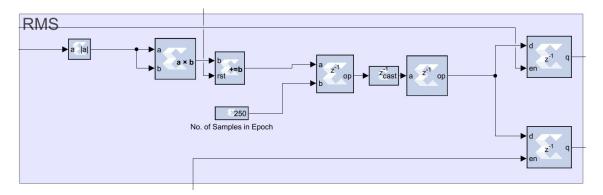

|   |      | 4.3.2 Feature Extraction Subsystem         | 65 |

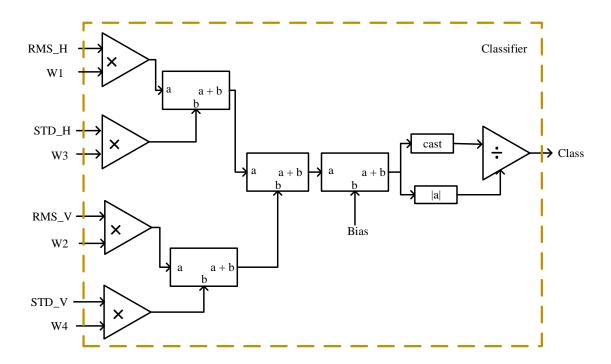

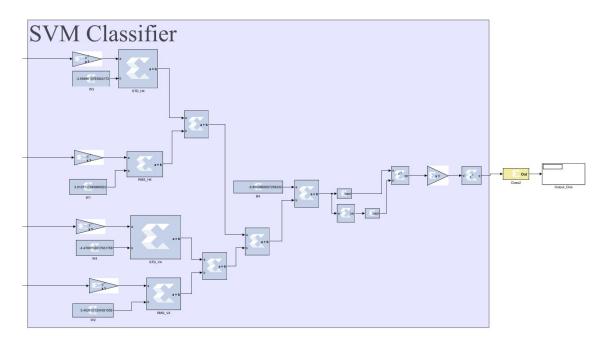

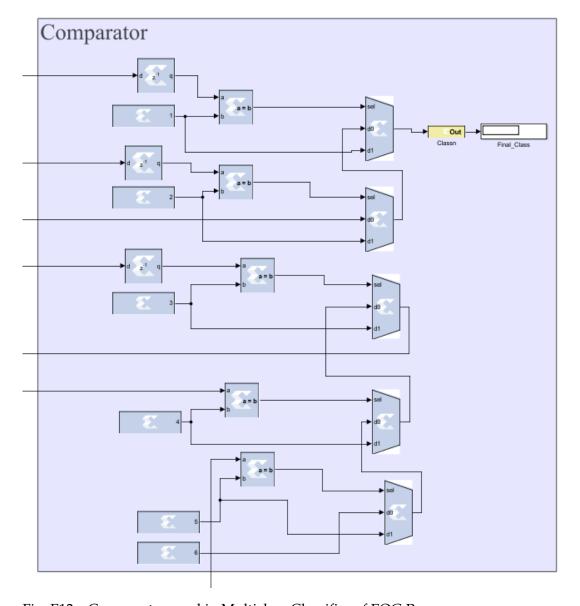

|   |      | 4.3.3 Classification Subsystem             | 68 |

|   | 4.4                  | Summary                                           | 71  |

|---|----------------------|---------------------------------------------------|-----|

| 5 | Performance Analysis |                                                   |     |

|   | 5.1                  | Performance analysis of Binary Classification     | 72  |

|   |                      | 5.1.1 Results                                     | 72  |

|   |                      | 5.1.2 Comparative Study                           | 81  |

|   | 5.2                  | Performance analysis of Multiclass Classification | 83  |

|   |                      | 5.2.1 Results                                     | 83  |

|   |                      | 5.2.2 Comparative Study                           | 90  |

|   | 5.3                  | Summary                                           | 92  |

| 6 | Con                  | aclusions                                         | 93  |

|   | 6.1                  | General Summary                                   | 93  |

|   | 6.2                  | Key Findings                                      | 94  |

|   | 6.3                  | Limitation of the study                           | 96  |

|   | 6.4                  | Future Research Directions and Opportunities      | 96  |

| 7 | Bib                  | liography                                         | 97  |

| 8 | App                  | pendices                                          | 114 |

# **List of Figures**

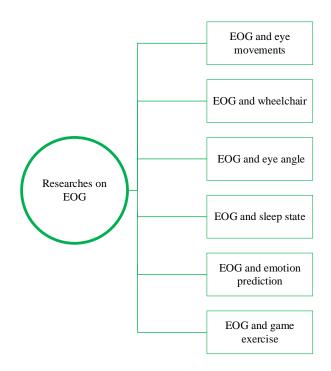

| Fig. 1.1 | Classification of researches on EOG                               | 4  |

|----------|-------------------------------------------------------------------|----|

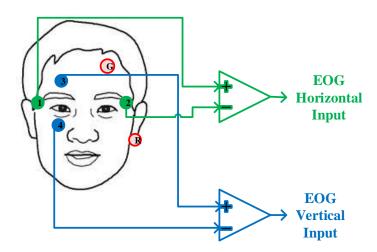

| Fig. 1.2 | A typical dual channel data acquisition of EOG signals            | 4  |

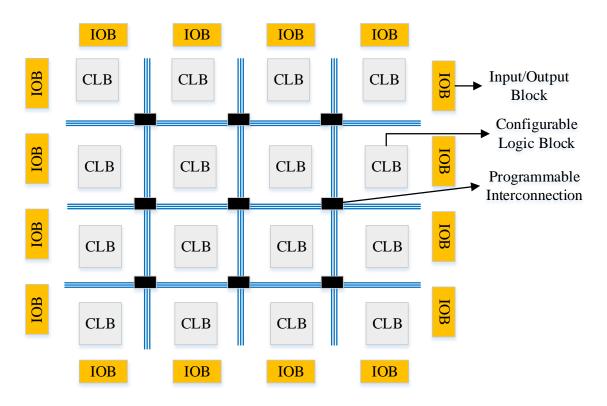

| Fig. 1.3 | Basic structure of an FPGA chip                                   | 8  |

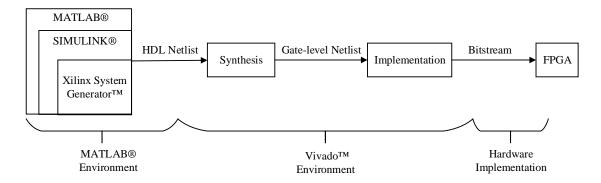

| Fig. 1.4 | Design flow of FPGA implementation using XSG                      | 12 |

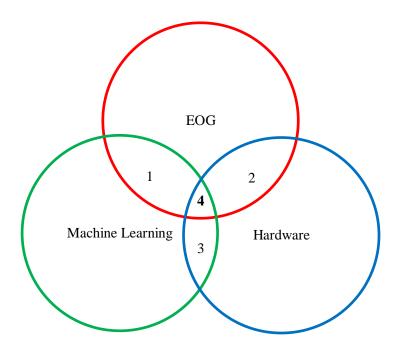

| Fig. 1.5 | A ven diagram illustrating the present state of the problem       | 12 |

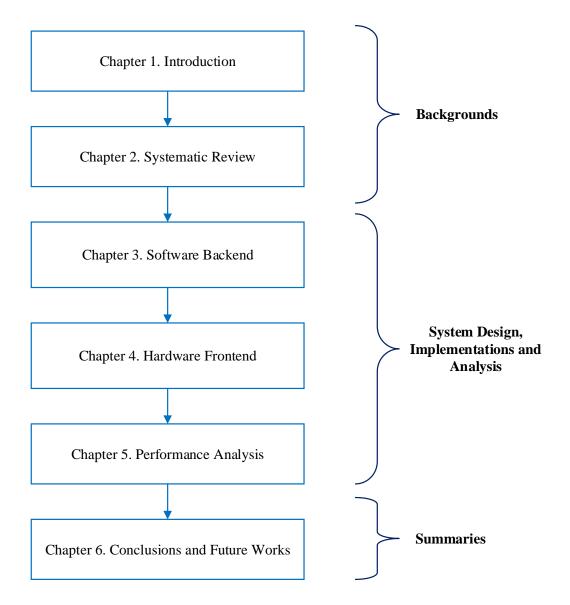

| Fig. 1.6 | Structure of the thesis                                           | 15 |

| Fig. 2.1 | Importance of point-of-care testing system                        | 18 |

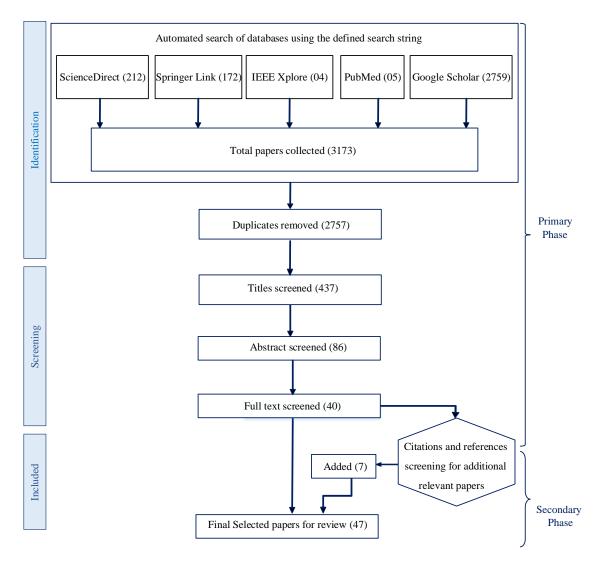

| Fig. 2.2 | PRISMA flow diagram for the initial study selection of the sys-   |    |

| tem      | atic review                                                       | 20 |

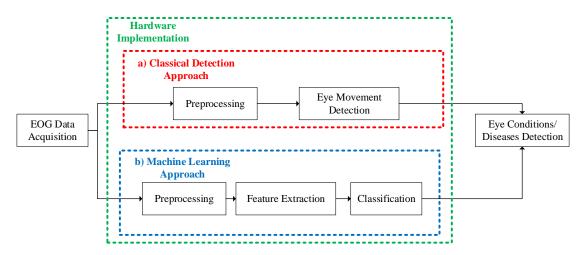

| Fig. 2.3 | Hardware implementation of EOG processor                          | 23 |

| Fig. 2.4 | Ratio of EOG signal implementations in different hardware         | 24 |

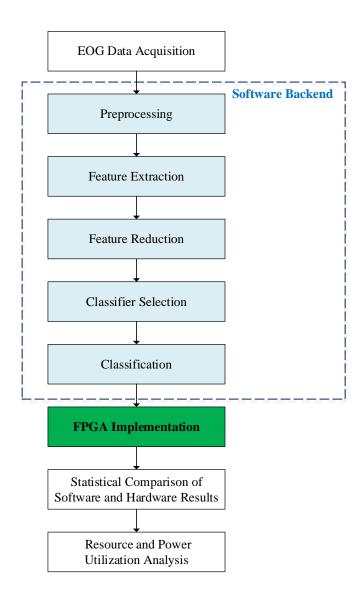

| Fig. 3.1 | Basic steps of designing FPGA implemented EOG processor           | 40 |

| Fig. 3.2 | Simplified block diagram of the complete system at the software   |    |

| leve     | el                                                                | 41 |

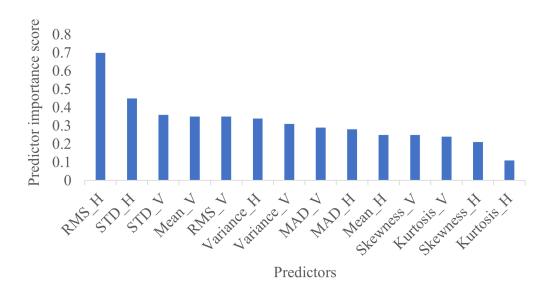

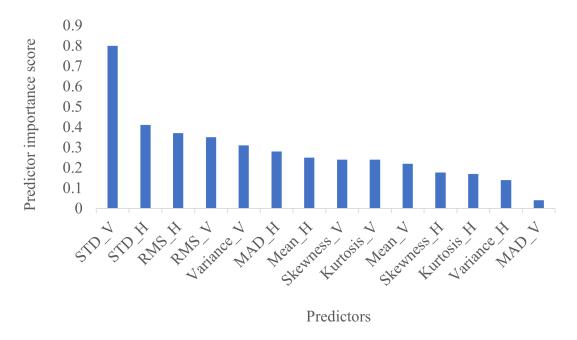

| Fig. 3.3 | Predictor importance score for features in binary classification  | 48 |

| Fig. 3.4 | Predictor importance score for features in multiclass classifica- |    |

| tion     | ı                                                                 | 49 |

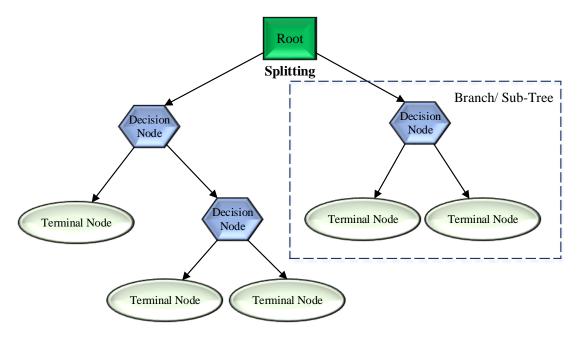

| Fig. 3.5 | Tree classifier                                                   | 51 |

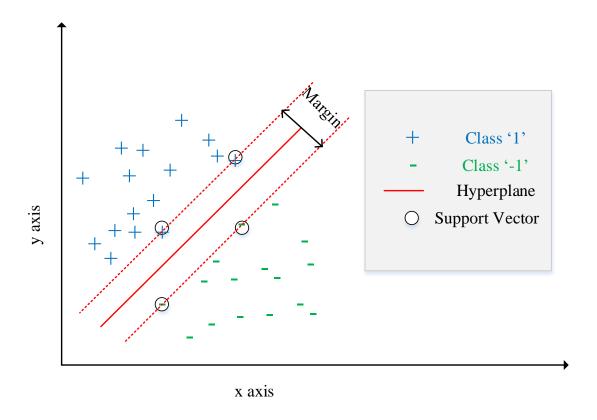

| Fig. 3.6 | Boundary between two classes defined by a hyperplane in SVM       | 52 |

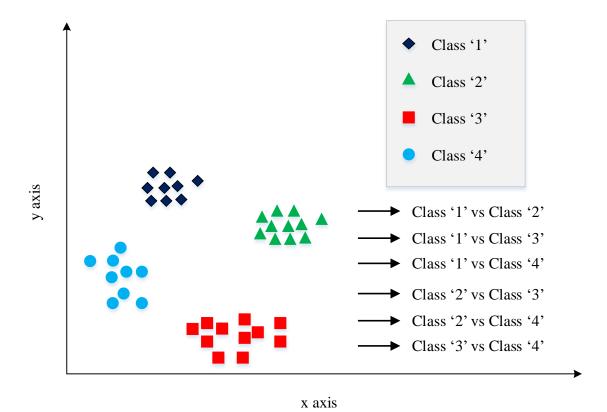

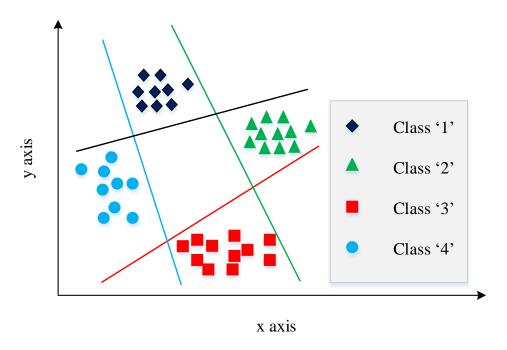

| Fig. 3.7 | One-vs-One approach in multiclass SVM                             | 54 |

| Fig. 3.8 | One-vs-All approach in multiclass SVM                             | 55 |

| Fig. 4.1 | Block diagram of the FPGA implemented system for Binary clas-     |    |

| sific    | cation                                                            | 61 |

| Fig. 4.2 | Block diagram of the FPGA implemented system for Multiclass       |    |

| clas     | sification                                                        | 62 |

| Fig. 4. | Block diagram of the preprocessing subsystem                        | 64 |

|---------|---------------------------------------------------------------------|----|

| Fig. 4. | 4 Normalization of the preprocessed EOG signals                     | 65 |

| Fig. 4. | Block diagram of the RMS calculator in feature extraction sub-      |    |

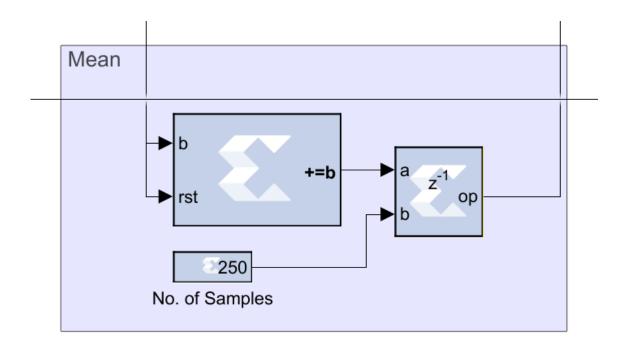

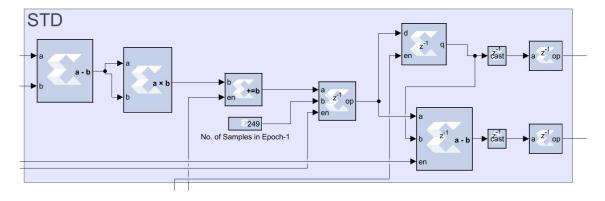

| s       | ystem                                                               | 66 |

| Fig. 4. | 6 Block diagram of the STD calculator in feature extraction subsys- |    |

| t       | em                                                                  | 67 |

| Fig. 4. | 7 Block diagram of the Binary Classifier                            | 68 |

| Fig. 4. | 8 Block Diagram of the Multiclass Classifier                        | 70 |

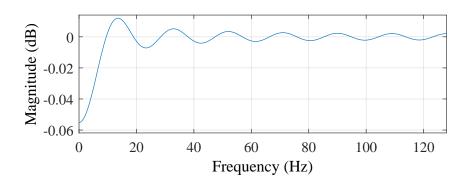

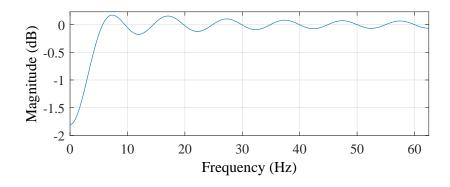

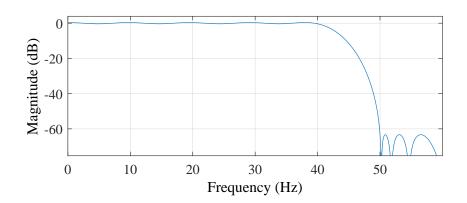

| Fig. 5. | 1 Magnitude Response of High-pass filter in hardware                | 72 |

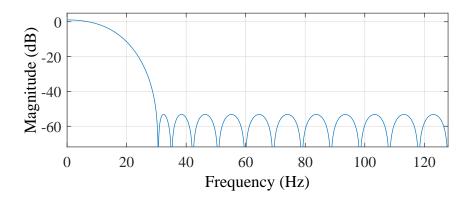

| Fig. 5. | 2 Magnitude Response of Low-pass filter                             | 73 |

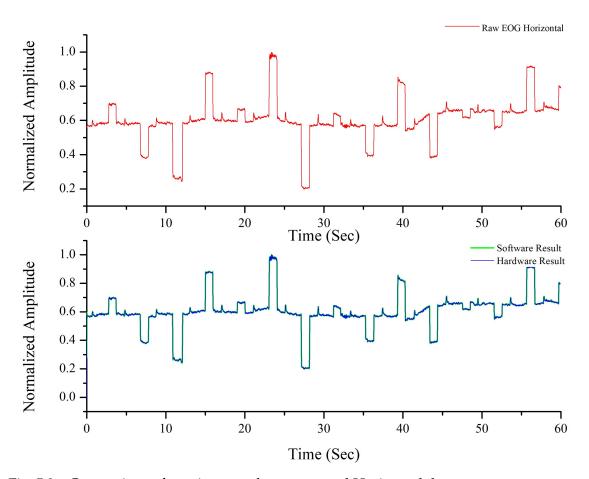

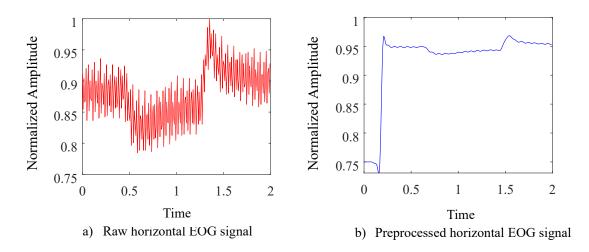

| Fig. 5. | 3 Comparison of raw input and preprocessed Horizontal data          | 73 |

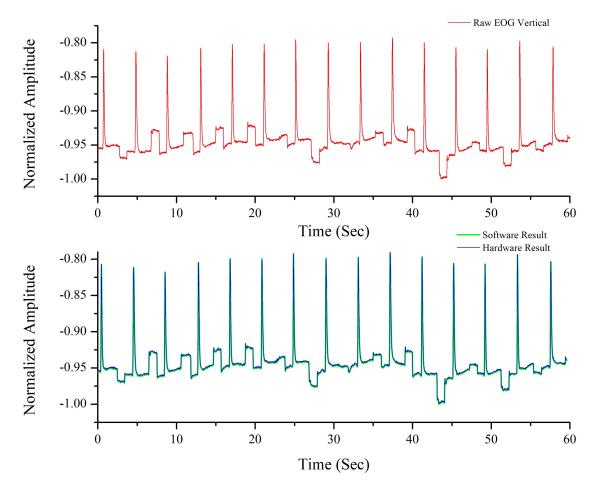

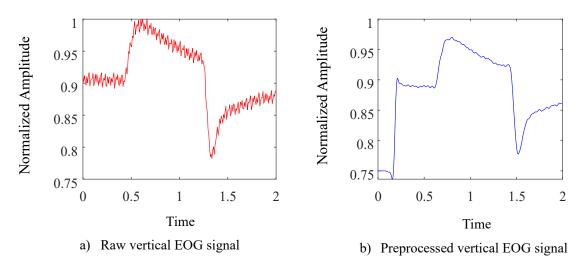

| Fig. 5. | 4 Comparison of raw input and preprocessed Vertical Data            | 74 |

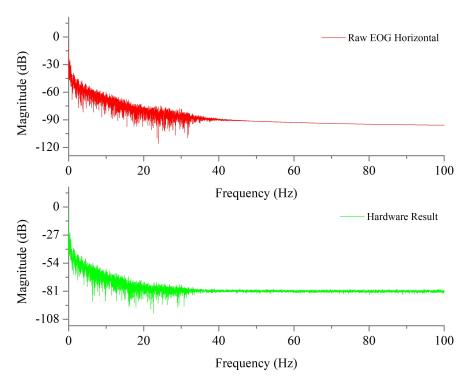

| Fig. 5. | 5 Comparison of the frequency response of input and hardware ou     | t- |

| p       | ut for Horizontal Data                                              | 75 |

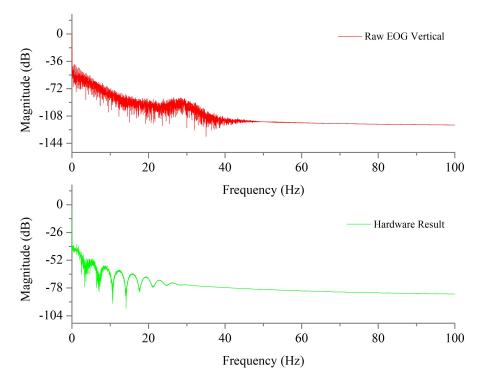

| Fig. 5. | 6 Comparison of the frequency response of input and hardware ou     | t- |

| p       | ut for Vertical Data                                                | 75 |

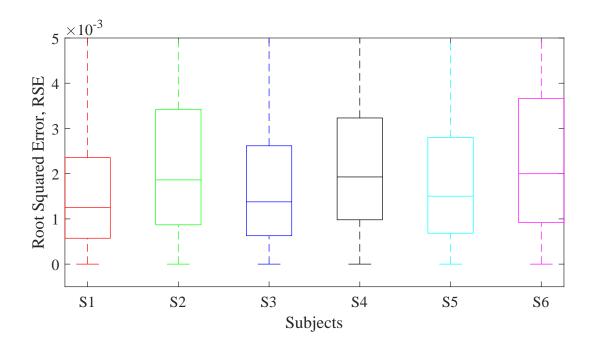

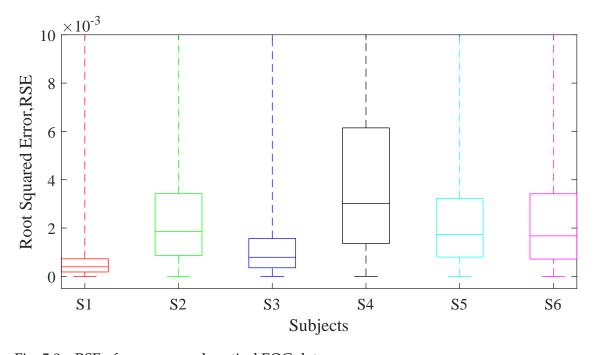

| Fig. 5. | 7 RSE of preprocessed horizontal EOG data                           | 77 |

| Fig. 5. | RSE of preprocessed vertical EOG data                               | 77 |

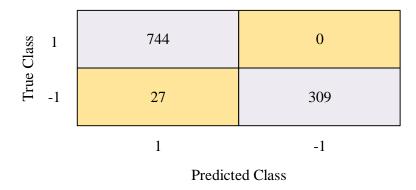

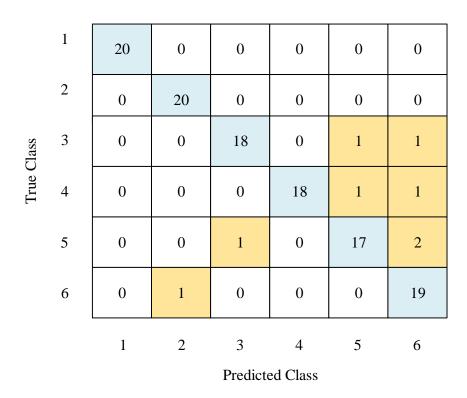

| Fig. 5. | Onfusion matrix for binary classification in software               | 78 |

| Fig. 5. | 10 Confusion matrix for binary classification in hardware           | 79 |

| Fig. 5. | 11 Manitude response of high pass filter                            | 83 |

| Fig. 5. | 12 Manitude response of low pass filter                             | 83 |

| Fig. 5. | 13 Raw and preprocessed horizontal EOG signal                       | 84 |

| Fig. 5. | 14 Raw and preprocessed vertical EOG signal                         | 84 |

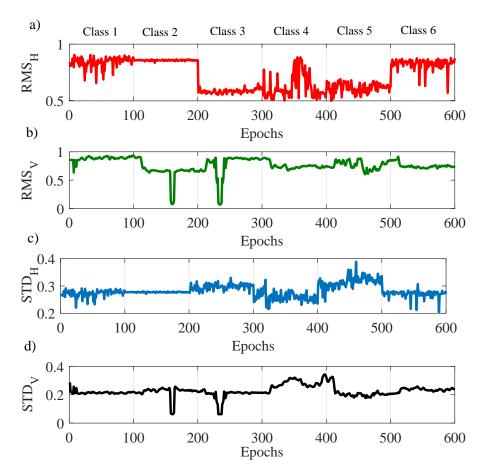

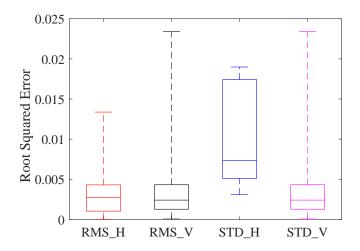

| Fig. 5. | 15 Features of EOG signals (a) RMS of EOG_h, (b) RMS of EOG_v,      |    |

| (       | c) STD of EOG_h,and (d) STD of EOG_v                                | 86 |

| Fig. 5. | 16 Root Squared Error between software and hardware outputs in      |    |

| fe      | eature extraction stage                                             | 86 |

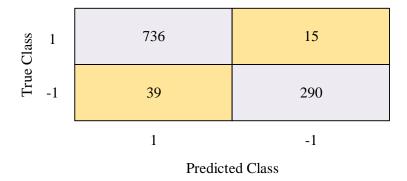

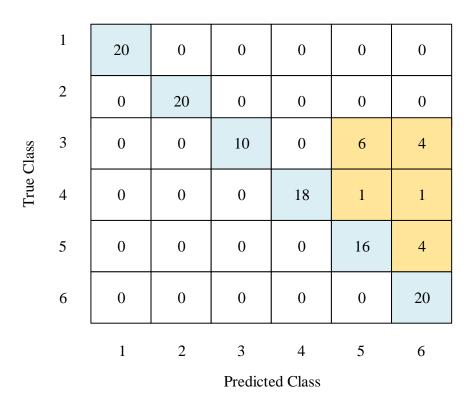

| Fig. 5. | 17 Confusion matrix for multiclass classification in software       | 87 |

| Fig. 5. | 18 Confusion matrix for multiclass classification in hardware       | 88 |

# **List of Tables**

| Table 2.1 | A summary of EOG acquisition process                               | 22 |

|-----------|--------------------------------------------------------------------|----|

| Table 2.2 | A summary of FPGA implementation of EOG                            | 26 |

| Table 2.3 | A summary of reconfigurable EOG preprocessing techniques           | 27 |

| Table 2.4 | A summary of non-configurable hardware implementations of          |    |

| EOG       |                                                                    | 29 |

| Table 2.5 | A summary of present state-of-the-art EOG eye movement de-         |    |

| tectio    | on approaches                                                      | 30 |

| Table 3.1 | Specifications of filters for Binary and Multiclass classification | 43 |

| Table 3.2 | Software accuracies for different classifiers                      | 50 |

| Table 4.1 | Selection of processing approach for different stages              | 63 |

| Table 5.1 | The Pearson Correlation Coefficient in preprocessing stage of      |    |

| Bina      | ry Classification                                                  | 76 |

| Table 5.2 | FPGA resource utilization in ZedBoard for binary classification    | 80 |

| Table 5.3 | FPGA power consumption in Zedboard for binary classifica-          |    |

| tion      |                                                                    | 80 |

| Table 5.4 | Comparative study of state-of-the-art works of EOG based blin      | k  |

| detec     | ction                                                              | 82 |

| Table 5.5 | The Pearson Correlation Coefficient in preprocessing stage of      |    |

| Mult      | iclass Classification                                              | 85 |

| Table 5.6 | Performance analysis of Multiclass classifier                      | 88 |

| Table 5.7 | Comparison of testing accuracy of multiclass classifier in soft-   |    |

| ware      | and hardware                                                       | 89 |

| Table 5.8 | FPGA resource utilization in Zynq UltraScale+ for multiclass       |    |

| class     | ification                                                          | 89 |

| Table | 5.9    | FPGA power consumption in Zynq UltraScale+. for multiclass       |     |

|-------|--------|------------------------------------------------------------------|-----|

|       | classi | fication                                                         | 90  |

| Table | 5.10   | Comparative study of machine learning based EOG reconfig-        |     |

|       | urabl  | e implementation                                                 | 91  |

| Table | C1     | Parameters of Binary Classifier of EOG Signal Processor for Blir | ık  |

|       | Detec  | ction                                                            | 120 |

| Table | C2     | Parameters of Multiclass Classifier of EOG Signal Processor for  |     |

|       | Multi  | iclass Eye Movement Detection                                    | 120 |

## Nomenclature

### **Abbreviations**

BRAM = Block Random Access Memory

CPLD = Complex Programmable Logic Device

DSP = Digital Signal Processor

EEG = Electroencephalogram

EMG = Electromyogram

EOG = Electroculogram

FF = Flipflop

FN = False Negative

FP = False Positive

FPGA = Field Programmable Gate Array

LUT = Lookup Table

LUTRAM = Lookup Table Random Access Memory

RMS = Root Mean Square

RSE = Root Squared Error

POC = Point of Care

SoC = System on chip

SPLD = Simple Programmable Logic Device

STD = Standard Deviation

SVM = Support Vector Machine

TN = True Negative

TP = True Positive

XSG = Xilinx System Generator

# **List of Symbols**

```

b = \text{Bias}

f = \text{Frequency}

\mu = \text{Mean}

\sigma = \text{Standard Deviation}

\mathbf{x} = \text{Feature Vector}

\mathbf{W} = \text{Vector containing Weights of Features}

C_n = \text{Output of Classifier n}

```

# **Chapter 1: Introduction**

Electrroculogram (EOG) is an electrophysiological signal. This signal provides insights into eye movement patterns and eye-related conditions. EOG-based digital systems can assist people in various fields such as medical professionals, researchers, and developers working on assistive technologies and human-computer interaction. Domain-specific reconfigurable signal processors like field programmable gate arrays (FPGAs) are often desirable in such applications to ensure real-time signal analysis, resource optimization, and point-of-care usage. In this research, state-of-the-art EOG signal processors are thoroughly studied to identify contemporary research dynamics. In this thesis, two novel prototypes are designed to answer a few research questions found in the academic literature. This chapter gives a brief review of EOG signals, EOG data acquisition methods, and various eye movements. An overview of FPGA is also discussed. This chapter outlines the background in Section 1.1, the present state of the problem in Section 1.2, and specific objectives in Section 1.3. Section 1.4 describes the significance and scope of this research. Finally, Section 1.5 includes an outline of the remaining chapters of the thesis.

### 1.1 Background

According to the World Health Organization (WHO), at least 1 in 6 people go through disability [1]. People from low-income countries are suffering more than others in this issue. WHO introduced the Global Cooperation on Assistive Technology (GATE) to ensure access to high-quality affordable assistive products worldwide [2]. In the last twenty-five years, progress in this sector has been praiseworthy. GATE has shown a great contribution to creating a supportive environment for disabled people. However, there is still a need for the advancement and use of rehabilitation and assistive technologies. Eyes can play a major contribution in the development of rehabilitation Engineering. Most of the physically disabled people can move their eyes only [3]. The development of eye movement-based technological devices can assist them directly[4]-[8].

The eyes are one of the most remarkable organs of human beings. Eyes contribute significantly to the perception of the world. Taking care of the eyes and addressing any vision issues promptly is essential for maintaining quality of life. The activity of various cells and structures within the eye produces biopotential through electrical signals. These electrical signals are essential for transmitting visual information from the retina to the brain. An electrooculogram, often abbreviated as EOG, is a diagnostic tool used in medical and scientific research to measure and record the electrical activity generated by the movements of a person's eyes. This non-invasive technique is valuable in understanding and analyzing eye movements, which can provide insights into various neurological and ophthalmological conditions. By monitoring the electrical potentials generated by the eye muscles, an EOG can help in diagnosing disorders such as nystagmus, strabismus, and other eye movement abnormalities. Additionally, EOGs have applications in the field of human-computer interaction, where they are used to control devices or interfaces through eye movements, making them a versatile tool with both clinical and technological significance. EOG can be utilized in automated cars to detect stress or drowsiness of the driver. Point-of-care (POC) systems can play an important role in the timely and accurate diagnosis, management, and treatment of eye conditions. Including EOG analysis in POCs has the potential to improve patient outcomes, increase access to eye care services, and enhance the overall efficiency of eye care delivery, making them an important component of modern healthcare systems. Modern technologies require fast, low-cost, and compact hardware devices that provide quick solutions to the user. These issuses can be addressed with a re-configurable approach, Field Programmable Gate Array (FPGA). In this thesis, hardware-software cosimulation is opted for as it verifies that hardware and software function correctly together. It helps to verify the functionality before building the final hardware. Therefore, this thesis aims to design EOG signal processor for detecting eye movements in FPGA. Subsection 1.1.1 describes EOG, EOG acquisition techniques, and various eye movement characteristics. It is also important to give an insight into FPGA, which is described later on in subsection 1.1.2. A brief description of the FPGA modules and the design tool are given in 1.1.3 and 1.1.4 respectively.

### 1.1.1 Electrooculogram

The eye can be considered as a dipole having its positive and negative poles at the cornea and retina respectively [9]. The eye has a steady corneo-retinal potential generated within the eyeball by the metabolically active retinal epithelium. The potential can be measured by placing electrodes on the skin surface around the eyes which is referred to as the electrooculography technique. This technique provides electrooculogram (EOG) which represents the recording of eye movements. The major advantages of EOG are that it is non-invasive and inexpensive [10]. Generally, the amplitude of EOG signals is in the 50 to 3500  $\mu$ V range[11]. The frequency of EOG signals can vary in the range of DC to 100 Hz [12]. However, useful EOG information can be extracted from the 0 to 30 Hz range or 0 to 40 Hz range [11,13]. These values can vary with the luminous intensity [13]. EOG contains some impulsive noises such as powerline interference, and baseline drift. Therefore, filters are used for canceling these noises in the preprocessing stage. The denoised EOG signals are then ready to be processed further to the application stage. EOG signals covers a broad area of applications and research. A classification of research on EOG is shown in Fig. 1.1. Research on EOG deals with classifying eye movements, eye angle, sleep state, predicting emotion, and developing wheelchairs, game exercises [14]. The research of EOG based eye movement detection is directly connected to various disease detections. For example, normal and abnormal eye movements play an important role in detecting neurodegenerative diseases [15], diagnosing attention deficit hyperactivity disorder [16] etc. Besides, eye movements help in the communication of disabled people translating their thoughts into words [17]. On the other hand, sleep disorder threatens the quality of health of people all around the globe. Sleep stage information from EOG can be utilized to solve this disease [18]. Classification of EOG is a major concern for the future development of multimode controllers, communication devices, and HCI [19]. Most of the work done for classifying EOG is based on software [20, 14]. However, the hardware implementation for providing compact and mobile solutions for disabled persons is also getting popular day by day [21, 22]. Therefore optimized hardware implementation of EOG is still an issue of research. EOG can be implemented at the hardware level using

Fig. 1.1 Classification of researches on EOG

discrte circuits, micro-controllers, Arduino, as well as reconfigurable devices like FPGA.

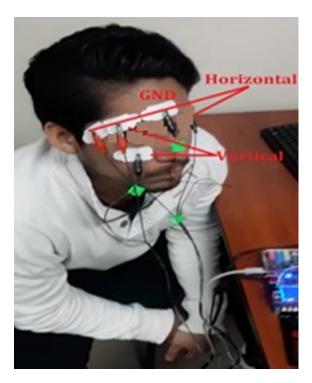

#### **EOG Data Acquisition Methods**

EOG data can be obtained by placing electrodes near the eyes. Generally, EOG data acquisition can be categorized into main two types: dual channel and single channel acquisition.

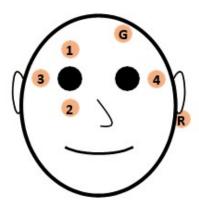

Fig. 1.2 A typical dual channel data acquisition of EOG signals

#### 1. Dual Channel

Dual channel EOG signals acquisition needs two pairs of electrodes. These electrodes are sensors to record the electrical activity from the eyes during eye movements. Here, two electrodes are placed on the horizontal sides of the eyes as shown by electrodes 1 and 2 in Fig. 1.2 and two electrodes i.e. electrodes 3 and 4 are placed above and under the right eye. The ground electrode, G is generally placed on the forehead and The reference electrode, G can be placed on the mastoid behind the left ear. The placement of reference electrodes can vary in individual works. Fig. 1.2 shows a dual channel electrode configuration. EOG signals contain horizontal and vertical components. The output from the electrodes provides the horizontal EOG signals,  $EOG_h$  and vertical EOG signals,  $EOG_v$  as given in equation 1.1 and equation 1.2 respectively.

$$EOG_h(t) = V_1(t) - V_2(t)$$

(1.1)

$$EOG_v(t) = V_3(t) - V_4(t)$$

(1.2)

Here,  $V_x(t)$  denotes the EOG potential recorded using electrode x where, x = 1, 2, 3, 4.

#### 2. Single Channel

Single channel EOG signals acquisition needs only one pair of electrodes. Horizontal EOG signals,  $EOG_h$  can be obtained by placing electrodes on two sides of the eyes as shown (green) in Fig. 1.2. On the other hand, the electrode pair placed above and under the eye as shown (blue) in Fig. 1.2 provides the single channel vertical EOG signals,  $EOG_v$ .

In addition to the main two EOG data acquisition techniques, there are some other techniques in the literature. Those include modified electrode configuration [23], eyeglasses [24], EOG sensors [25], optical sensors [26], contact lenses [27]. In this work, dual channel EOG data containing horizontal EOG signals and vertical EOG signals is used.

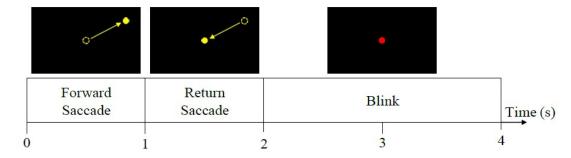

#### Eye movements

EOG provides the signal extracted from the electrode placed around the eyes. It reflects the movement of the eyes. Eye movements can be mainly categorized into three types: saccade, blink, and fixation.

#### 1. Saccade

Saccades can be represented as the movement of the eyes while viewing a visual scene. During this activity, simultaneous movement of both eyes is seen. Saccade duration ranges from 300 to 400 ms [28]. During this period the eyes abruptly change the point of fixation. Saccades play an important role in reading. They allow the eyes to move from one word and one line to the next. Saccades can be detected using eye-tracking technologies [24]

#### 2. Blink

Blinking can be defined as an automatic process of eyes getting open and closed. This is a rapid and repetitive movement of the eyelids. Eyebillinks are an integral part of the normal function of the eyes. This movement helps to spread a thin layer of tear film across the surface of the eye and ensures the moisture in eyes. Blinks also protect eyes from damage caused by excessive brightness by reducing the amount of light entering the eye. Generally, blinking occurs throughout the whole day. The average blink duration ranges from 100 to 400 ms [9]. The average blink rate can be 12 to 19 blinks per minute at rest. This rate can be influenced by environmental and physical factors. Environmental factors include temperature, relative humidity, and brightness. The physical factors include the health of the eyes, activity level, level of cognitive workload, or fatigue.

#### 3. Fixation

Fixation is the stationary state of the eyes. Fixations represent the interval between two saccades. Fixation time is the time to focus after stopping the eyeball which ranges from 100 to 200 ms [9]. This movement helps to construct a continuous and coherent visual perception. For example, during reading, fixations occur at each word in a text and process the visual information within each word.

In the literature, a good amount of work has been done with blink detection, classification of saccade and blink. In addition, to blink information, EOG signals can provide information on various eye movements such as: up, down, right, and left. These eye movements can be easily detected using EOG signals as the signals represent significant differences for different eye movements. Literary works show evidence that EOG signal processing for eye movement classification is getting more popular for human machine interfaces (HMIs). In this work, EOG is processed for blink detection, and eye movement classification that can further be used in other HMI applications.

### 1.1.2 Reconfigurable Computation Architecture- FPGA

Digital hardware systems can be implemented in various devices such as Field Programmable Gate Array (FPGA), Complex Programmable Logic Device (CPLD), Simple Programmable Logic Device (SPLD), microcontroller, and others.

In this work, FPGA is utilized to implement the designs at the hardware level because of its characteristics. FPGA refers to a type of integrated circuit that can be reconfigured or programmed after manufacturing to perform various digital logic functions. The reconfigurable architecture makes FPGA highly adaptable for various tasks. FPGAs are capable of parallel processing, which means they can perform multiple tasks simultaneously. This makes them suitable for tasks like signal processing, and real-time data analysis [29]. FPGAs have low latency and high throughput, making them suitable for applications that require fast data processing. FPGAs are valuable in the development and prototyping phases of electronic designs. FPGAs help in quick testing and iterating designs before committing to application specific integrated circuits (ASICs) or other fixed hardware. This custom-made circuit designing scheme ensures dynamic resource utilization to speed up data processing- the hardware acceleration. FPGAs are energy efficient, especially when compared to power-hungry Graphics Processing Units (GPUs). Because FPGAs execute tasks in hardware, they can often perform the same calculations with significantly lower power consumption. FPGAs also offer longer lifespans compared to off-the-shelf GPUs. Therefore, it can be said that FPGAs are a suitable choice when it is needed to ensure hardware customization,

low latency, and specialized acceleration for specific tasks.

Based on the advantages of FPGA, it can be useful in proof-of-concept designs. This kind of design helps to demonstrate whether an idea can be turned into a reality. Therefore, in this work, FPGA is chosen for developing the designs. FPGAs are typically programmed using Hardware Description Languages (HDLs) like Very High-Speed Integrated Circuit Hardware Description Language (VHDL) or Verilog. There are also higher-level programming tools and languages that make FPGA development more accessible. Before programming FPGA, it is needed to get insights into the basic structure of FPGA and its components.

Fig. 1.3 Basic structure of an FPGA chip

Figure 1.3 shows a typical internal structure of an FPGA chip. Generally, an FPGA consists of three basic components. They are:

- 1. Configurable Logic Blocks (CLB)- responsible for implementing the core logic functions.

- 2. Programmable Interconnection responsible for connecting the Logic Blocks.

3. Input/Output Blocks (IOB) – connected to the Logic Blocks through the routing and make external connections.

The logic functions of these blocks and the connections are given by the designer as needed. The CLB is the fundamental block in FPGA that contains flip-flops (FFs), look-up tables (LUTs), and multiplexers inside. FF refers to a binary register circuit that can store one bit. A flip-flop is the smallest storage resource on the FPGA. It can save logic states between clock cycles on an FPGA circuit. LUT represents a collection of gates hardwired on the FPGA. It can store a predefined list of outputs for every combination of inputs. LUTs provide a fast way to retrieve the output of a logic operation because possible results are stored and then referenced rather than calculated. A multiplexer represents a circuit that can select between two or more inputs and then return the selected input. There can be some other blocks such as memories (BRAMs, LUTRAMs, ROMs, shift registers), Digital Signal Processors (DSP), Phase-Locked Loop (PLL) clock generators, etc. in a modern FPGA.

#### 1.1.3 Module Selection

This thesis aims to implement EOG signals processor at the hardware level. Hardware based digital and embedded systems are becoming more popular due to their multifunction capability, low cost, and high-performance accuracy. FPGA has been chosen for this study as it is simple and easy to design as well as has the advantage of reprogrammable functionality. FPGA contains more logic blocks than CPLD or SPLD. It allows greater customization and more complex processes than CPLD and SPLD. Also, microcontroller provides reprogramming of firmware but FPGA has the advantage of changing the functionality of both hardware and firmware. FPGA has the advantage of hardware acceleration as it can be used to accelerate workloads and gain significant benefits. Parallel computing is another advantage of the FPGA which allows to handle multiple workloads. This provides the scope to work on different stages of tasks concurrently which cannot be done with GPUs. Some other advantages of FPGA are smaller board space, power efficiency, and reliability. Therefore, in this thesis, two FPGA modules: Zedboard Zynq-7000, and Zynq Ultrascale+ are chosen to implement the

designed works. A short description of the selected modules is given below.

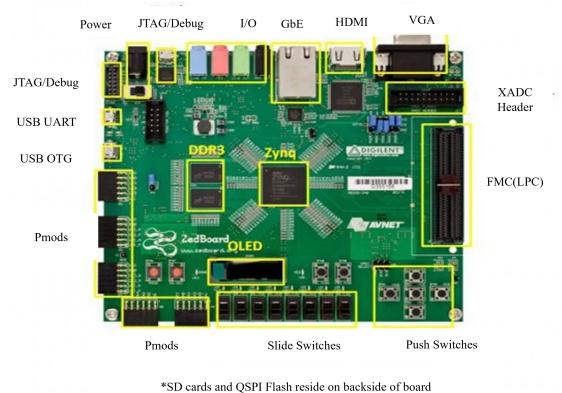

#### Zedboard Zynq-7000

ZedBoard is a low-cost development board manufactured by Digilent. This board employs Xilinx Artix-7 FPGAs coupled with a dual-core ARM Cortex-A9 processor [30]. The ZedBoard has a broad range of applications, such as digital signal processing (DSP), image processing, industrial automation, etc. This FPGA system-on-a-chip (SoC) based board enables the designers to accelerate the custom DSP algorithm, as it is possible to program Zedboard whenever necessary [31]. The first design of this thesis uses ZedBoard for hardware implementation.

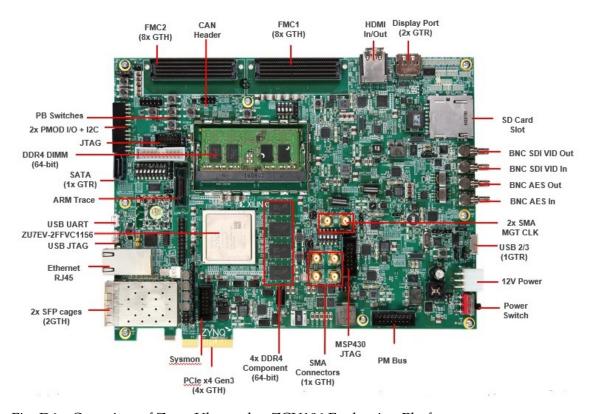

#### Zynq UltraScale+

The ZCU106 Evaluation Kit contains a Zynq<sup>™</sup> UltraScale+<sup>™</sup> MPSoC EV device and supports all major peripherals and interfaces, enabling development for a wide range of applications [32]. This kit is able to make designs for video conferencing, surveillance, Advanced Driver Assisted Systems (ADAS), streaming, and encoding applications. The included ZU7EV device is equipped with a quad-core Arm® Cortex®-A53 applications processor and a dual-core Cortex-R5 real-time processor. The second design of this thesis uses Zynq UltraScale+.

Appendix D provides a detailed description of the above-mentioned modules.

### 1.1.4 Design Tool Selection

The goal of this thesis includes hardware-software codesigning of the EOG signal processors. Hardware-software codesign refers to the concurrent designs of hardware and software components of complex electronic systems. These designs are capable of merging hardware and software that can ensure optimization, and satisfaction of the design constraints such as cost, performance, and power consumption. These types of designs can be very beneficial for real-life problems dealing with a pragmatic approach. The pragmatic approach checks the practical feasibility of a defined task. Therefore, the designs of this work use hardware-software codesign. For this design purpose, proper tool selection is necessary. In this thesis, the Xilinx system generator (XSG) is selected for design at the hard-

ware level. XSG is a design tool for the implementation of DSP algorithms in Xilinx devices. It is a MATLAB Simulink add-on that enables the development of architecture-level FPGA designs using graphical block programming. Xilinx FP-GAs platforms contain Block RAMs, DSP Slices, PCI Express support, and programmable fabric, etc. It is possible to process in both parallel and pipelining approaches as all of these compute resources can be used simultaneously. In XSG hardware description language is used to assemble FPGA building blocks into a circuit. This design is easier compared to typical high-level languages. The two most popular hardware description languages are VHDL and Verilog. In XSG the system is designed in Matlab Simulink and then synthesized the design into an FPGA. High-level synthesis (HLS) uses a high-level programming language like C, and C++ to describe the functionality of a digital circuit or electronic system. HLS tools then automatically convert this high-level description into a registertransfer level (RTL) hardware description, which can be implemented on programmable hardware such as FPGAs or ASICs. HLS helps in building and verifying hardware. Therefore, optimization of the hardware design is possible. The designer can design at a higher level of abstraction and the tool can complete the RTL implementation.

The design flow of FPGA implementation in Xilinx system generator is given in Figure 1.4. In Software co-simulation, all Xilinx blocks are connected between two blocks - Gateway In and Gateway Out, which behave as input and output respectively for the hardware design. The Xilinx blocks work with fixed point format, therefore, it is necessary to convert real-world signals of floating format into the fixed point and vice versa. In this case, Gateway In and Gateway Out blocks act as translators for format conversion.

After software simulation, the System Generator token needs to be configured to allow the model to be compiled into hardware. The XSG token dialog box needs to be configured with adequate settings for compilation, synthesis, and clocking. At first, the compilation Target is chosen by specifying the FPGA platform. After that, the synthesis tool is involved in synthesizing the design. It includes setting some parameters such as hardware language, clock etc. After the configuration, a bit stream (.bit) file is generated. Then, the hardware co-simulation target is se-

Fig. 1.4 Design flow of FPGA implementation using XSG

lected and a block will be generated. This block can be then added to the design and all the blocks for both software and hardware can considered to be co-exist. In this work, firstly ZedBoard is chosen to implement the binary classification. Then, Zynq Ultrascale+ is chosen to implement the multiclass classification. Both modules are designed using XSG.

### 1.2 Present State of the Problem

Fig. 1.5 A ven diagram illustrating the present state of the problem

In this section, the present state of the problem for EOG hardware implementations is depicted. The world is heading towards point-of-care testing systems. Blinks and eye movements detected from the EOG signal are utilized to determine various eye conditions. EOG signals are being studied through machine learning for various eye condition analyses and disease detection which is indicated by the "area 1" in Fig. 1.5. There are some works of EOG that include hardware implementations as indicated by "area 2". There are studies that include hardware implementation without using machine learning as given in "area 3". However, as machine learning is getting more popular day by day, more focus on the combination of machine learning & re-configurable hardware implementation of EOG signals is more demanding nowadays. A common platform of machine learning, EOG hardware implemented works are indicated in "area 4". These can be utilized for digital point-of-care systems. These type of implementations includes the design and implementation of various stages: preprocessing, feature extraction, and classification. Efficient designs need optimization throughout each stage. Therefore, the need for compact and optimized hardwarebased systems for eye movement detection arises to overcome this issue. This thesis addresses the issue by providing proof-of-concept complete digital systems for blink and various eye movement detection.

## 1.3 Specific Objectives

Eye movement is a frequent physiological activity of human beings. It possible to collect information on these eye movements by processing EOG signals . An efficient algorithm to process EOG is important to integrate it into point-of-care devices and human machine interfaces (HMIs) applications. It is also important to choose a suitable platform to implement the algorithmic design. Therefore, hardware-software codesign can be the proper solution to verify the EOG signal processing algorithm. However, these algorithm needs to be hardware-friendly i.e. the algorithms must be designed in a way to use few resource blocks, consume low power, and offer low time delay.

Field Programmable Gate Array (FPGA) can be a suitable platform to implement digital signal processing algorithms because of its characteristics: low cost, low power consumption, re-configurable architecture, small size, and high speed.

This work aims to codesign hardware-software multichannel FPGA-based complete EOG processors adopting a machine learning approach. The designed processors detect eye blinks and various eye movements. The implemented stage includes: preprocessing, feature extracting, and classifying.

The specific objectives of this thesis are as follows:

- 1. To develop hardware-friendly algorithms to classify the EOG signals.

- 2. To design compact systems of EOG processors on FPGA using the developed algorithms.

#### 1.4 Contribution of the Work

EOG signals provide insights into eye movement patterns. Many existing works of EOG deal with eye movement detections, and eye conditions and disease detections based on the the detected eye movements. This thesis provides the first systematic review of EOG hardware implementations to provide an idea on exisiting reasearch opportunities. Digital systems of EOG signals can be helpful for classifying blinks and eye movements. This thesis provides hardware-software codesign of the blink detector and the eye movement classifier using EOG signals. Blink detectors can be readily integrated with human machine interfaces. The eye movement detector can pave the way for eye e-health as this system will open the door for other diseases to be detected from eye movements.

### 1.5 Thesis Outline

The thesis presents the design of the software backend and the hardware frontend of systems dedicated to electrooculogram (EOG) signal processing. The EOG signal processors are designed as binary classifier for blink detection and mutliclass classifier for detecting six different eye movements. The overall thesis organization is depicted in Fig. 1.6. This thesis contains a total of six chapters. A brief description of these chapters is given below.

Chapter 1 describes the background of the EOG signal first. After that, the method of EOG signal acquisition, and basic eye movements are explained. The problem

Fig. 1.6 Structure of the thesis

statement and significance of the study are also discussed.

Chapter 2 reviews the application of EOG signals in various sectors. The previous works on EOG signals are discussed. A systematic review is presented on EOG hardware implementations. The systematic review is focused on providing a structured discussion on solely EOG based point of care systems.

Chapter 3 shows the software backend for the design of the EOG binary classifier for blink detection and the EOG multiclass classifier for six eye movements detection.

Chapter 4 shows the hardware frontend design of the EOG binary classifier for blink detection and the EOG multiclass classifier for six eye movements detection. It shows the FPGA implementation approach. The system architecture of hardware design of various subsystems in Xilinx system generator are explained Chapter 5 represents the performance analysis of the designed processors. It includes both software and hardware performance and checks their agreements. Resource utilization and power consumption analysis are given in this chapter. The comparative study with previous works is also presented.

Finally, Chapter 6 presents the conclusions of the thesis and summarizes the overall contribution of this research. Some scopes of possible future works are also mentioned at the end.

# **Chapter 2: Systematic Review**

The eyes can be a great tool to assist disabled people with technological devices run by eye movements. The hardware-implemented platform increases feasibility in this area. Eye diseases are one of the major contributors to disabling conditions. Negligence in regular checkups is the key reason for deteriorating eyesight. The high cost of checkups for disease detection is another reason for not regularly receiving health check-ups. Consequently, these diseases ultimately turn severe and can take severe form, leading to blindness. A preventive health checkup can prevent the disease from worsening and save many people from losing their working ability. Around 2 billion people face vision impairment and various ocular diseases worldwide. Efficient hardware can provide quick decisions for emergency medical services, remote medical care, and intensive care. The goal of providing emergency and fast services can be achieved through point-of-care (POC) systems. In this chapter, at first, some real-life applications of electrooculogram are outlined. Then, the advantages of the POC systems are outlined. A systematic review approach is employed to review the state-of-the-art works on EOG hardware systems. A systematic review is a rigorous and comprehensive method of summarizing and synthesizing existing research evidence on a specific research question or topic. This chapter includes the method and findings of the review.

### 2.1 Electrooculogram Applications in Real-Life

The eyes are an integral part of the human body. It helps disabled people to communicate with the external world by using eye movements [5]-[8]. The assistive devices developed based on eye movements are great tools to ease their life. Additionally, eye diseases also contribute to creating disabling conditions. There are various diseases such as nystagmus, ocular dysfunction, and dry eyes that can be detected just by using Electrooculogram (EOG) signals [33]-[37]. These diseases primarily cause blurriness. In the long run, they can cause blindness

leading to vision disability. Efficient hardware can provide quick decisions for eye movement detections. Thus, hardware-implemented platforms are necessary to be developed for both rehabilitation purposes and point-of-care systems.

## 2.2 Electrooculogram Point-of-care Systems

Point-of-Care (POC) means the point in time when healthcare services and products are being provided to patients at the time of care [38]. POC systems are important as they provide some advantages such as early screening leading to early diagnosis, separating inpatients & out-patients, critical & non-critical patients, monitoring recovery, and finally providing early recovery to immunity. Some examples of POC systems are home pregnancy tests, blood glucose monitors, and urine dipsticks etc. Fig. 2.1 outlines the importance of the POC testing

Fig. 2.1 Importance of point-of-care testing system

system. Obtaining signals from eyes by electrooculography and implementing

them at the hardware level can pave the way for POC systems for various eye conditions detection.

### 2.3 Methodology of Systematic Review

In this study, a systematic review process [39] to find the research trend and the state of the art of EOG hardare implementations to develop EOG point of care (POC) systems. The review is conducted following the Preferred Reporting Items for Systematic Reviews and Meta-Analyses (PRISMA) protocol and the Problem, Intervention, Comparison, and Outcomes (PICO) statement [40, 41]. The PRISMA flow diagram and the number of publications of each stage are shown in Fig. 2.2. The focus is given to the works solely based on EOG excluding hybrid works of EOG. The search string includes classification and hardware as EOG point of care systems use hardware applications based on classification. Studies containing hybrid works of EOG and any other signal, non-human subjects (e.g., animals), and non-English papers are excluded.

The review process is done mainly in two phases: primary and secondary phases as shown in Fig. 2.2. These phases are described below.

### 2.3.1 Primary Phase

In the primary phase, identification and screening of the research articles are done.

#### 1. Identification

This stage involves investigating related studies based on the search string in selected databases. The papers are extracted from major science-related databases, namely ScienceDirect, Springer Link, IEEE Xplore, PubMed, and Google Scholar.

The search string used is defined as: (EOG AND Classification AND (FPGA

Fig. 2.2 PRISMA flow diagram for the initial study selection of the systematic review

### OR Hardware) NOT Hybrid).

The searches have been done between the 5th–15th of May 2023 and covered publications in the range of 2018–2023. Selected papers are written in English and from conferences and journals. A total of 3173 papers have been collected from this search. Then, the duplicates are removed using the EndNote tool. Then, 2757 papers were used for screening in the next stage.

#### 2. Screening

The screening depends on the titles and abstracts in the database. Duplicate articles have been first removed and further screening is carried out on the remaining selected papers. Articles have been excluded if 1) have hy-

bridization of EOG with any other signal, and 2) have no information about the hardware implementations. EndNote tool is used to analyze and screen the papers. To qualify the conformity and correspondence, the abstract-screened articles are then subjectively screened by authors. After the full-text screening, 40 papers have been selected.

### 2.3.2 Secondary Phase

Sanka and Cheung [42] recommended a combination of both the automated search and a manual search in systematic reviews. Therefore, in the secondary phase, the references and citations of the 40 selected papers of the primary phase are checked. After screenings, 7 more relevant papers are added to the initial 40 selected papers. Finally, a total of 47 papers are included for the review.

### 2.3.3 Research Findings

51% of the studies are journal papers and the rest 49% are conference papers. EOG studies cover classifying eye movement, eye angle, sleep state, predicting emotion, and developing wheelchairs, and game exercises as mentioned in section 2.1. At first, the studies are categorized based on the data acquisition techniques: dual channel, single channel, and others. Then, based on the detection or classification techniques can be categorized in the studies: classical detection approach and machine learning approaches. Then, hardware implementations are categorized based on the hardware used as reconfigurable (FPGA) and nonconfigurable. These categories are briefly described in the subsequent sections. Among the selected papers, 59% of works study with dual channel data while 29% on single channel. Also, 12% of them worked on other types of data acquisition which includes Eyeglasses [24], EOG sensors [25], Biosensors [43], Optical sensors [26], Capacitive sensing [44], Smart glasses with EOG sensors [45], Magnet [46]. Modified single channel has used two electrodes in a little bit of changed position [23]. Table 2.1 shows the summary of the EOG acquisition process.

Table 2.1: A summary of EOG acquisition process

| Method         | References                                                       |

|----------------|------------------------------------------------------------------|

|                | Rotariu et al. [10], Das et al. [11], Asanza et al. [13],        |

|                | Fernandez et al. [15], Latifoglu et al. [16],                    |

|                | Kishore Kumar and Narayanam [20],                                |

|                | Chowdhury et al. [21], Borkar et al. [22],                       |

| Dual Channel   | Hou and Smitha [47], Shivaprasad and Vishwanath [48],            |

|                | Kabir et al. [49], Golparvar and Yapici [50],                    |

|                | Abdel-Samei et al. [51], Archana et al. [52], Lin et al. [53],   |

|                | Parra et al. [54], Gundugonti and Narayanam (2021) [55],         |

|                | Anuradha et al. [56], Zou and Zhang [57], Hossieny et al.        |

|                | [58], Lopez et al. (2018)[59], and Martínez-Cerveró et al. [60]  |

| Single Channel | Zaeni et al. [19], Daou et al. [43], Archana et al. [52],        |

| (Horizontal)   | Fan et al. [61], Simoes et al. [62],                             |

|                | Prabha et al. [63], Lopez et al. (2019) [64], Bastes et al. [65] |

| Single Channel | Molina-Cantero et al. [17], and Hayawi and Waleed [66]           |

| (Vertical)     |                                                                  |

|                | Savastaer and Tepe [23] (Modified), Ryu et al. [24] (Eye-        |

|                | glasses), Pai et al. [25] (EOG sensors),                         |

| Others         | Masai et al. [26] (Optical sensors), Li et al. (2022)[27] (Con-  |

|                | tact lens), Daou et al. [43] (Biosensors), Matthies et al. [44]  |

|                | (Capacitive sensing), Li et al. (2020) [45](Smart glasses), and  |

|                | Almansouri et al. [46] (Magnet)                                  |

## 2.4 Detection Approaches

After data acquisition, the data needs to be preprocessed for denoising the EOG signal. The unwanted noises such as baseline wander, and 50/60 Hz power line interference needs to be eliminated in this stage. Then the data is processed further for classification. EOG classifications or detection approaches are found mainly in two categories:- classical detection approaches and machine learning approaches.

Classical detection approaches need preprocessing and suitable movement algorithm as shown in Fig. 2.3 (Red box). A basic block diagram of EOG processing using machine learning and deep learning is shown in Fig. 2.3 (Blue box). The raw EOG data must go through preprocessing, feature extraction and classification stages.

Fig. 2.3 Hardware implementation of EOG processor

In literature, 42% of the works are found to adopt classical detection approaches whereas the rest 58% adopt machine learning approaches. It indicates the recent trend of EOG signal processing with machine learning approaches.

## 2.5 Hardware Implementations of EOG

The implementation level of the selected studies has been categorized into two: FPGA and discrete circuits or micro-controllers.

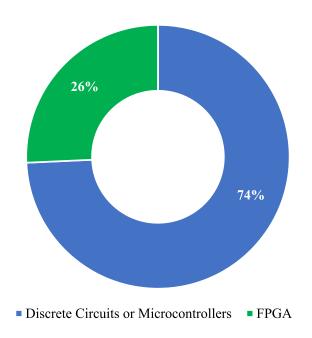

More than three-fourths (26%) of the works were implemented on FPGA which involves the process of determining the physical resources of FPGA and utilizing them. The rest of the works (74%) were implemented on discrete circuits or microcontrollers as shown in Fig. 2.4.

It is complex to implement systems efficiently on FPGA as it requires some expertise. Despite the tendency of FPGA to consume more power than a microcontroller or an ASIC, FPGA requires a smaller board space and shows energy efficiency than the equivalent discrete circuit. FPGA based implementations also provide some benefits over others as they provide the flexibility of reconfiguring the design.

Fig. 2.4 Ratio of EOG signal implementations in different hardware.

### 2.5.1 FPGA based EOG Implementations

Cano et al. [67] developed an efficient design a convolutional neural network and implemented it on FPGA device. Fernandez et al. [15] designed a FPGA based system for the generation of multiple visual stimulus signals and for EOG acquisition. Kumar and narayanam (2020a) [68] developed a denoising filter with differential evaluation (DE) algorithm with fewer sign power of two which was verified using Altera DSP Builder. Kumar et al. [69] proposed a modified FIR filter using Canonical signed digit (CSD) and Kumar and Narayanam (2020b) [70] proposed a modified FIR filter using canonical signed digit representation and compressor techniques for denoising the EOG signal. In both works, the proposed models were implemented and verified on FPGA. Gundugonti and Narayanam (2021) [55] ]developed an architecture of the discrete Haar wavelet transform which was synthesized using Cadence RTL compiler. Kishore Kumar and Narayanam [20] detected the saccades and blinks. They denoised the EOG signals with transposed direct form FIR filter. The Haar wavelet transform was

used for decomposition of denoised EOG signal. The modified eye movement detection algorithm was synthesized on FPGA. Gundugonti and Narayanam (2022) [71] proposed area and power efficient FIR filter structure using common subexpression elimination (CSE) algorithm with CSD method which was later verified in Xilinx-Simulink environment. Asanza et al. [13] used preprocessing and feature extraction in software level. They developed a custom hardware architecture for EOG classification model in al FPGA card. Das et al. [11] proposed a reconfigurable preprocessing technique using FIR and IIR filters for serial processing of EOG horizontal and vertical data and implemented it in Xilinx Zynq-7000 FPGA Table 2.3 summarizes FPGA Implementation of EOG. As it is seen, preprocessing stage is currently being implemented in FPGA. It is noticeable that there is a scope for extracting the features in a reconfigurable platform. The advantages and limitations of the reconfigurable processing techniques are summarized in Table 2.3.

Das et al. [11] proposed a design to implement a fast EOG serial preprocessor using FIR and IIR filters. The Pearson Correlation Coefficient of 0.99 and a Mean Root Squared Error in the  $10^{-3}$  range were found. The on-chip power consumption for this design was 0.271 watts. The limitation was a delay because of serial processing which was minimized by using a fast counter. Kumar and Narayanam (2020a); Kishore Kumar and Narayanam [68, 20] used a filter with differential evolution (DE) algorithm. The mian advantage of this filter was using fewer sign-power-of-two (SPT) terms to optimize the denoising filter. This hardware used less area than conventional filters. The limitation of their work was that the coefficients were best suitable for Application-specific integrated circuit (ASIC) implementations only. Kumar and Narayanam (2020b) [70] proposed FIR architecture that uses canonical signed digit-based (CSD) multipliers and 3:2 or 4:2 compressors to achieve greater improvement in power and delay compared to the conventional shift-add method of multiplication. CSD was used to reduce the multiplication's design complexity by representing the filter coefficients in

Table 2.2: A summary of FPGA implementation of EOG

| Algorithm                      | CNN              | 1                                | 1                                | 1                 | Haar DWT                             | Haar DWT                        | 1                                    | Cubic SVM          | 1               |

|--------------------------------|------------------|----------------------------------|----------------------------------|-------------------|--------------------------------------|---------------------------------|--------------------------------------|--------------------|-----------------|

| Classification<br>or Detection | <i>&gt;</i>      | ×                                | ×                                | ×                 | >                                    | >                               | ×                                    | >                  | ×               |

| Feature<br>Extraction          | ×                | ×                                | ×                                | ×                 | ×                                    | ×                               | ×                                    | ×                  | ×               |

| Preprocessing                  | ×                | >                                | >                                | >                 | ×                                    | >                               | >                                    | ×                  | >               |

| References                     | Cano et al. [67] | Kumar and Narayanam (2020a) [68] | Kumar and Narayanam (2020b) [70] | Kumar et al. [69] | Gundugonti and Narayanam (2021) [55] | Kishore Kumar and Narayanam[20] | Gundugonti and Narayanam (2022) [71] | Asanza et al. [13] | Das et al. [11] |

Table 2.3: A summary of reconfigurable EOG preprocessing techniques

| Preprocessing Techniques                | Advantages                                  | Limitations           | References                                                  |

|-----------------------------------------|---------------------------------------------|-----------------------|-------------------------------------------------------------|

| FIR & IIR Filter<br>(Serial Processino) | Almost half resource of traditional designs | Delay                 | Das et al. [11]                                             |

| Filter with                             | Fewer SPT terms,                            | Best suitable for     | Kumar and Narayanam (2020a) [68] &                          |

| DE algorithm                            | less area, low power                        | ASIC implementation   | Kishore Kumar and Narayanam [20]                            |

| FIR filter                              | Reduced delay                               | High area and power   | Kumar and Narayanam (2020b) [70]                            |

| (CSD+compressor)                        | •                                           | )                     |                                                             |

| Filter (CSE + CSD)                      | Low power & area                            | Delay                 | Kumar et al. [69] &<br>Gundugonti and Narayanam (2022) [71] |

| DWT                                     | Low resource utilization                    | Shift sensitivity and | Meeravali et al. [72]                                       |

|                                         |                                             | poor directionality   |                                                             |

CSD format. The final designed filter provided reduced delay but the area and power are higher than CSD. Kumar et al. [69], and Gundugonti and Narayanam (2022) [71] used an area and power efficient filter for real-time noise reduction of EOG using a common sub-expression elimination method. This filter architecture offered a 148.17% area increment and a 114.45% power increment over traditional filter architecture. However, the delay is higher than [70]. Meeravali et al. [72] developed an efficient wavelet-based architecture for denoising EOG signals. However, it showed shift sensitivity and poor directionality.

## 2.5.2 Other implementations of EOG

This section gives an overview of the non-configurable implementation of EOG processing of the selected works. Table 2.4 summarizes the implementation of discrete circuits and micro-controllers and eyewear. They have some advantages such as low time requirement for performing the operation, ease of use, simple troubleshooting and system maintenance, and flexibility due to their small size. Microcontrollers for the data acquisition stage is prominently seen in state-of-the art literature [10,16,19,21,22,26,46,48,49,51,52,63,65]. Discrete circuits and microcontrollers are utilized for data acquisition and processing stages [23,44,50,54]. Pai et al. [25] used a prototype with EOG sensor. Masai et al. [26] used a smartwear with sensors. Jins meme smartglasses are found to be used for data acquisition [45, 73,74].

## 2.6 State-of-the-Art

The EOG hardware implementations cover a large area. In this section, the performance of the state-of-the-art studies that only deal with eye movement detection is outlined. Table 2.5 summarizes the accuracy of the various techniques used in the studies.

Rotariu et al. [10] utilized dual channel EOG to develop an electronic medical de-

Table 2.4: A summary of non-configurable hardware implementations of EOG

| Hardware            | Implemented stage                                           | References                                                                                                                                                                                                                                                                 |

|---------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Micro-controllers   | Data acquisition                                            | Rotariu et al. [10] Borkar et al. [22] Bastes et al. [65] Chowdhury et al. [21] Shivaprasad and Vishwanath [48] Kabir et al. [49] Latifoglu et al. [16] Zaeni et al. [19] Almansouri et al. [46] Archana et al. [52] Lopez et al. (2018) [59] Martínez-Cerveró et al. [60] |

|                     | Classification                                              | Prabha et al. [63], Daou et al. [43]                                                                                                                                                                                                                                       |

|                     | Data acquisition                                            | Savastaer and Tepe [23]                                                                                                                                                                                                                                                    |

| Discrete circuits & | Data acquisition with sensors                               | Matthies et al. [44]<br>Masai et al. [26]                                                                                                                                                                                                                                  |

| micro-controllers   | Data acquisition (Discrete circuits), Processing ( $\mu$ C) | Parra et al. [54]                                                                                                                                                                                                                                                          |

|                     | Data acquisition & Processing                               | Golparvar and Yapici [50]                                                                                                                                                                                                                                                  |

|                     |                                                             | Abdel-Samei et al. [51]                                                                                                                                                                                                                                                    |

|                     |                                                             | Pai et al. [25]                                                                                                                                                                                                                                                            |

|                     |                                                             | Masai et al. [26]                                                                                                                                                                                                                                                          |

| Others              | Data acquisition & Processing                               | Li et al. (2020) [45]                                                                                                                                                                                                                                                      |

|                     |                                                             | Rostaminia et al. [73]                                                                                                                                                                                                                                                     |

|                     |                                                             | Yeo at al. [74]                                                                                                                                                                                                                                                            |

|                     |                                                             | Li et al. (2022) [27]                                                                                                                                                                                                                                                      |

|                     |                                                             |                                                                                                                                                                                                                                                                            |

Table 2.5: A summary of present state-of-the-art EOG eye movement detection approaches

| Approach  | Algorithm             | Accuracy          | Reference                     |

|-----------|-----------------------|-------------------|-------------------------------|

|           | Threshold             | 90%               | Rotariu et al. [10]           |

|           | Threshold             | -                 | Borkar et al. [22]            |

|           | DFT                   | 90%               | Bastes et al. [65]            |

|           | DOSbFC                | 94%               | Ryu et al. [24]               |

|           | Threshold             | 89%               | Hou & Smitha [47]             |

|           | Threshold             | 96% to 98%        | Chowdhury et al. [21]         |